Новые микроконтроллеры фирмы STMicroelectronics на базе ядра ARM Cortex-M3

|

|

|

Около 175 моделей от четырех производителей

|

|

|

11 июня 2007 года фирма STMicroelectronics анонсировала выпуск нового семейства 32-разрядных Flash микроконтроллеров STM32. Семейство было разработано с учетом требований, предъявляемых к встраиваемым приложениям:

малое энергопотребление, высокая производительность и низкая цена. В основе новых микроконтроллеров – продукт сотрудничества компаний STMicroelectronics и ARM – процессорное ядро ARM Cortex M3. Что обещает новая архитектура, каковы особенности семейства STM32 компании STMicroelectronics?

Ядро CORTEX-МЗ

В основу нового семейства положен продукт давнего сотрудничества фирм STM и ARM - ядро Cortex-МЗ, анонсированное в октябре 2004 года. Это ядро спроектировано для встраиваемых приложений, «чувствительных к цене», - контроллеров, автомобильных систем, бытовой техники и сетевых устройств. Микроконтроллеры STM32 являются первыми представителями семейства Cortex.

Ядро Cortex имеет три модификации:

- Cortex-A - для прикладных процессоров, работающих под управлением сложных ОС и пользовательских приложений;

- Cortex-R - основа встраиваемых процессоров для систем реального времени;

- Cortex-M - для микроконтроллеров и экономичных приложений;

В семействе Cortex впервые применен новый набор инструкций Thumb-2, который обеспечивает повышенную производительность и плотность кода и одновременно позволяет снизить энергопотребление ядра. Thumb-2 является развитием набора команд Thumb, применявшихся в прежних моделях ядер фирмы ARM, и сохраняет обратную совместимость с существующими решениями.

Набор инструкций Thumb позволял экономить память программ за счет более компактного хранения 16-разрядного кода. Однако полный набор инструкций ARM - таких как специальные команды типа SIMD, доступа к регистрам сопроцессора или использования привилегированных функций - не поддерживался. Кроме того, для выполнения той или иной задачи требовалось большее количество Thumb-инструкций (по сравнению с инструкциями ARM), что снижало быстродействие приложения. Поэтому программисты зачастую были вынуждены находить компромисс между размером кода и производительностью. При жестких ограничениях на объем памяти иногда приходилось выполнять несколько компиляций, подбирая баланс «размер кода/производительность» итеративно.

Для устранения недостатков Thumb набор инструкций Thumb-2 был усовершенствован. В него добавлены:

- новые 16-разрядные Thumb-инструкции для улучшенного управления ходом программы;

- новые 32-разрядные Thumb-инструкции, заменяющие 32-разрядные ARM-инструкции;

- новые 32-разрядные инструкции для повышения производительности и для обработки данных.

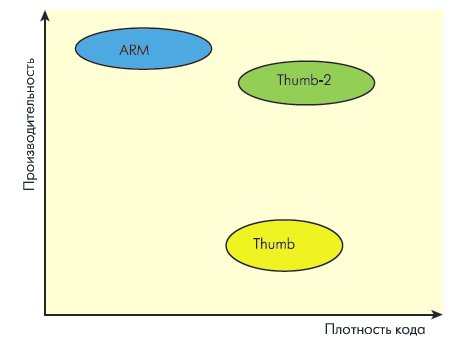

Добавлены инструкции для доступа к регистрам сопроцессора и специальным функциям SIMD, а также привилегированные функции, дающие, в отличие от предыдущей версии Thumb, доступ ко всем ресурсам процессора. Предусмотрен доступ ко всем ARM-инструкциям, введено и 12 полностью новых инструкций, улучшающих баланс «размер кода/производительность». Таким образом, Thumb-2 обеспечивает и повышенную производительность (процессор работает лишь на 2% медленнее, чем при использовании кода, компилированного с языка Си в код ARM-инструкций), и лучшую плотность кода (в среднем на четверть меньше, чем при использовании ARM-инструкций). По сравнению с Thumb, код Thumb-2 на 5% компактнее и на 2-3% быстрее (рис.1). Нововведения упростили разработку программ и сделали ненужным совместное использование ARM- и Thumb-кода. Так, ядро Cortex-M, в отличие от ядер Cortex-A и Cortex-R, вообще поддерживает лишь набор инструкций Thumb-2 (это первый случай, когда ARM выпустила ядро без обратной совместимости по коду).

Рис. 1. Соотношение производительности и плотности кода для наборов инструкций ARM, Thumb и Thumb-2

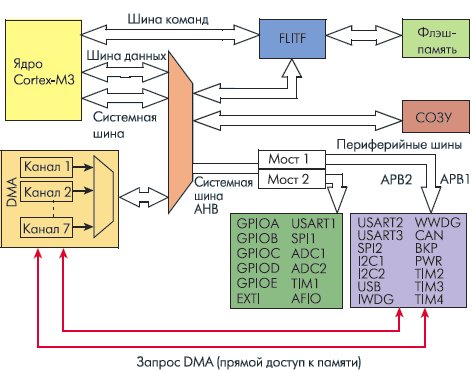

Ядро Cortex построено по гарвардской архитектуре с разделением шины данных и кода (рис.2). Это повышает производительность благодаря распараллеливанию выборки инструкций и загрузки данных. Кроме того, предусмотрен конвейер с тремя уровнями: выборка инструкции, декодирование и выполнение. Благодаря блоку предсказания ветвлений при выполнении данных операций на стадии декодирования происходит предварительная выборка инструкции, что также повышает быстродействие на этапе ветвления на один такт.

Рис. 2. Архитектура ядра Cortex-M3

Таблица 1. Сравнение ядер ARM7DTMI и ARMCortex-M3

| Параметр |

ARM7TDMI |

ARM Cortex-M3 |

| Архитектура |

ARMv4T (Фон Неймана) |

ARMv7 (Гарвардская)

|

| Набор инструкций |

Thumb/ARM |

Thumb/Thumb-2 |

| Конвейер |

3 уровня |

3 уровня + предсказание ветвлений |

| Прерывания |

FIQ/IRQ |

NMI (немаскируемые) + от 1 до 240 физических источников прерываний |

| Длительность входа в обработчик прерывания |

24-42 цикла |

12 циклов |

| Длительность переключения между обработчиками прерываний |

24 цикла |

6 циклов |

| Режимы пониженного энергопотребления |

Нет |

Встроены |

| Защита памяти |

Нет |

Блок защиты памяти с 8 областями |

| Производительность по тесту Dhrystone |

0,95 DMIPS/МГц (ARM)

0,74 DMIPS/МГц (Thumb) |

1,25 DMIPS/МГц |

| Энергопотребление ядра |

0,28 мВт/МГц |

0,19 мВт/МГц |

| Площадь кристалла |

0,62 мм2 (ядро) |

0,86 мм2 (ядро + периферия) |

Ядро поддерживает два режима работы: потоковый и режим обработчика исключений. Также организовано два режима доступа к коду. Это позволяет применять сложные и открытые системы, не жертвуя безопасностью приложений. Непривилегированное выполнение кода исключает доступ к потенциально «опасным» инструкциям и областям памяти. Штатный режим выполнения инструкций - потоковый, при котором поддерживается привилегированное и непривилегированное выполнение кода. Режим обработчика исключений включается при возникновении исключений, и здесь код выполняется в привилегированном режиме.

В ядре реализован прямой доступ к отдельным битам данных. В адресной области предусмотрено два 1-Мбайт блока с битовой адресацией и 32 Мбайт области регистров периферии. Если в системах на базе ядра ARM7 поддерживался только доступ к данным, выровненным по границам слов, то Cortex-МЗ способно передавать данные за единственный доступ к ядру без привязки к границам слов. На самом деле при использовании невыровненной выборки происходит несколько фоновых выборок в границах слов, но для программиста эта операция выглядит прозрачной.

Ядро Cortex-МЗ поддерживает 32-разрядные операции умножения, которые выполняются за 1 цикл (деление со знаком (SDIV) или без (UDIV) занимает от 2 до 12 тактов в зависимости от размера операндов).

Следующий важный блок ядра - контроллер вложенных прерываний. Здесь, в отличие от банков теневых регистров в ARM7, в целях повышения гибкости используется стековая модель. При возникновении исключения значения программного счетчика, регистров состояния, связи и общего назначения помещаются в стек. Шина данных хранит значения регистров в стеке, пока на шине инструкций определяется вектор исключения (из таблицы векторов) и производится выборка первой инструкции обработчика исключения. После выполнения кода обработчика происходит автоматическое восстановление состояния и продолжение выполнения прерванной программы. Таким образом, в обработчике прерываний исключается необходимость ассемблерных вставок для манипуляций со стеком, как это делалось при написании обработчиков прерываний на языке Си.

Также благодаря поддержке вложенных прерываний возможно динамическое изменение приоритетов прерываний даже во время выполнения какого-либо обработчика. Риск повторного вызова по прерыванию исключен благодаря блокировке до окончания выполнения текущей процедуры обработки.

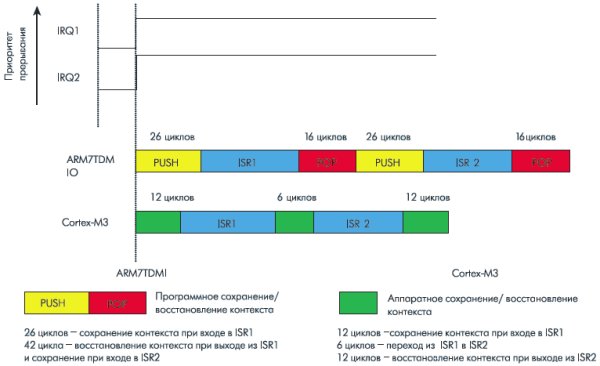

В случае последовательного или вложенного вызова обработчиков прерываний обычные системы повторяют операцию по сохранению и восстановлению регистров дважды. Это приводит к увеличению задержек при обработке прерываний - до 30 циклов. В ядре Cortex-МЗ переход между последовательно выполняемыми обработчиками сокращен до 6 циклов благодаря автоматическому сохранению контекста. Это особенно важно в системах с тактовыми частотами менее 100 МГц. На рис.3 показано сравнение схем работы контроллеров вложенных прерываний ядра Cortex-МЗ и ядра AR-M7TDMI, а в таблице приведены сравнительные характеристики процессоров на базе этих ядер.

Рис. 3. Работа контроллера вложенных прерываний

Программное обеспечение для ядра ARM7TDMI в большинстве случаев может быть перенесено на ядро Cortex-МЗ без существенных модификаций. Если приложение использует операционную систему реального времени (RTOS), которая портирована на Cortex-МЗ, или программа написана с использованием только языка Си, то переход может быть выполнен путем минимальных операций по перекомпиляции программ. Приложение, написанное на ассемблере и использующее только Thumb-инструкции, также будет работать на Cortex-МЗ. Если же используются ARM-инструкции, то с помощью программного средства Unified Assembler Framework можно эффективно преобразовать их в эквивалентные инструкции Thumb-2.

Микроконтроллеры STM32

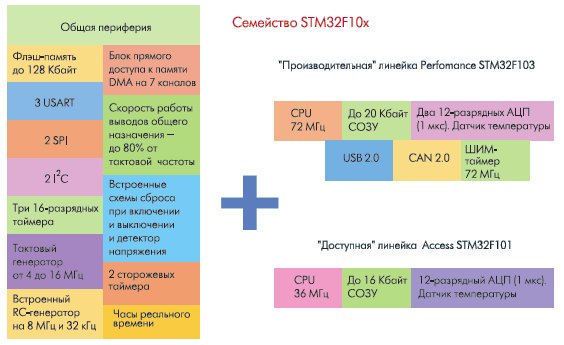

На момент написания статьи STM анонсировала две линейки микроконтроллеров семейства STM32, основанные на ядре Cortex-M3: STM32F1 0Зхх Performance ("производительная") с тактовой частотой до 72 МГц и богатым набором периферии, и STM32F101xx Access ("доступная") - с тактовой частотой до 36 МГц.

Обе линейки совместимы по выводам и имеют одинаковые объемы Flash памяти, не говоря уже о полной программной совместимости. Обе линейки STM32 предлагаются в трех типах корпусов LQFP48, LQFP64 и LQFP100 и имеют соответственно 32,49 и 80 линий ввода/вывода, толерантных к 5-В логике. На рис.4 дана схема, указывающая общие блоки и различия в периферии этих линеек.

Рис. 4. Семейство микроконтроллеров STM32

Приведем некоторые параметры периферии:

- скорость передачи данных по USB - 12 Мбит/с;

- скорость передачи данных по USART - до 4,5 Мбит/с;

- тактовая частота шины SPI - до 18 МГц, режим - ведущий или ведомый;

- тактовая частота шины l2C - до 400 кГц;

- скорость переключения выводов - до 18 МГц;

- частота ШИМ - до 72 МГц.

Память

Статическое ОЗУ (SRAM), расположенное на кристалле микроконтроллеров STM32, работает на частоте ядра без циклов ожидания, а встроенная Flash память позволяет хранить код и данные. Объем статического ОЗУ в линейках Performance и Access - от 10 до 20 Кбайт и от 6 до 16 Кбайт соответственно, а объем Flash памяти во всех линейках - от 32 до 128 Кбайт.

Обработка прерываний

Микроконтроллер оснащен контроллером вложенных векторных прерываний NVIC и контроллером внешних прерываний EXTI. Помимо 16 каналов прерываний, предусмотренных архитектурой ядра МЗ, контроллер NVIC поддерживает до 43 маскируемых каналов прерываний, которые могут работать с 16 уровнями приоритета. Это позволяет добиться чрезвычайно малого времени отклика на событие. Контроллер EXTI содержит 19 детекторов фронтов импульсов. Каждый детектор может быть независимо настроен на срабатывание от короткого импульса, а также от нарастания и спада фронта. При этом длительность импульса может быть короче периода периферийной внутренней шины АPB2. К линии детектора внешнего прерывания может быть подключен любой из 80 выводов общего назначения. Это позволяет выбрать собственную конфигурацию источников внешних событий.

Источники тактового сигнала

По умолчанию источником тактового сигнала является встроенный RC-генератор на частоту 8 МГц. Помимо него, можно использовать внешнее тактирование частотой от 4 до 16 МГц, причем в случае сбоя этого источника запустится программная обработка прерывания. Несколько предумножителей позволяют настроить частоту высокоскоростной системной шины АНB, высокоскоростной периферийной шины АPB2 и низкоскоростной периферийной шины АPB1. Максимальная частота системной шины и ядра составляет 36 МГц для линейки Access и 72 МГц - для Performance.

Кроме того, для тактирования ядра можно использовать встроенный RC-генератор с тактовой частотой 32 кГц и схемой ФАПЧ. Для работы часов реального времени предусмотрен отдельный генератор на 32 кГц с калибровкой.

Микроконтроллеры оснащены 16-разрядными таймерами (от одного до трех), каждый из которых имеет до четырех линий захвата и может быть сконфигурирован для работы в режиме сравнения, Ш И М-модулятора или счетчика импульсов. Для повышения надежности предусмотрены два 16-разрядных сторожевых таймера - независимый, тактируемый от независимого тактового генератора, и оконный. Имеется также специализированный SysTick-таймер, предназначенный для работы с операционной системой.

Выполнение кода

Предусмотрено три режима загрузки микроконтроллера: из встроенной Flash памяти, SRAM или системной памяти. Последний режим используется для загрузки пользовательской программы во Flash память по последовательному интерфейсу USART.

Супервизор питания

Встроенный детектор низкого напряжения питания (PVD) всегда активен и производит сброс микроконтроллера при падении напряжения ниже 2 В. Это позволяет отказаться от использования внешней схемы сброса.

Для сохранения хода часов и содержимого регистров при отключении питания имеется вход Vbat для подключения батареи.

Режимы пониженного энергопотребления

Для понижения энергопотребления предусмотрены три режима: Sleep, Stop и Standby.

В режиме Sleep ядро остановлено, а вся периферия работает, и при возникновении прерывания запускает ядро.

В режиме Stop микроконтроллер имеет самое низкое энергопотребление при сохранении содержимого ОЗУ и регистров. Все тактовые схемы, кроме часов реального времени, остановлены. Выход из этого режима возможен при возникновении внешнего прерывания на EXTI, прерывания от PVD, по сигналу от часов реального времени и сигналу «пробуждения» от шины USB.

В режиме Standby, в отличие от режима Stop, не сохраняется содержимое ОЗУ и регистров, кроме специализированных регистров управления. Выход их этого режима происходит при возникновении сигнала сброса, переполнении сторожевого таймера, положительном фронте на выводе WKUP или сигнале от часов реального времени.

DMA-контроллер

Контроллер прямого доступа к памяти (DMA) позволяет выполнять передачи типа память-память, память-периферия и периферия-память. В контроллере реализован кольцевой буфер, что позволяет избежать возникновения прерывания при достижении границы буфера. Каждый канал обслуживается отдельным DMA-запросом с поддержкой отдельных программных флагов для одного канала. Контроллер поддерживает работу всех основных блоков периферии - SPI, l2C, USART, таймеров и АЦП.

АЦП

Встроенный 12-разрядный АЦП со временем преобразования 1 мкс имеет 16 каналов. Диапазон входных напряжений АЦП - от 0 до 3,6 В. Кроме того, в микроконтроллер встроен температурный датчик, который можно подключить к АЦП.

Поддержка разработок

Фирма STM не оставляет разработчика «один на один» с новым микроконтроллером. На сайте www.st.com/stm32 размещены обширные библиотеки программ. Среди них - и примеры программ по управлению периферией, и библиотека для разработки программ и драйверов для работы с USB, и библиотека для управления различными электродвигателями.

Ядро Cortex-МЗ поддерживается компиляторами многих средств разработки, таких как IAR, Keil, Raisonance, Hi-tex, а также бесплатными средствами на базе GCC. Кроме того, для этого процессора портирован бесплатный проект FreeRTOS.

Для того чтобы сразу начать освоение нового процессора STM32 и отладку программ, компании STМ и Olimex подготовили также отладочные и стартовые наборы разработчика.

Выпустив новое семейство на базе Cortex-МЗ одной из первых, компания STM подтвердила статус новатора и амбициозного производителя электронных компонентов для той части рынка электронных устройств, которой требуются недорогие, но эффективные и экономичные микроконтроллеры. Учитывая общую тенденцию к выравниванию цен на 8-, 16- и 32-разрядные микроконтроллеры, можно рассматривать STM32 как отличную возможность легкого и обоснованного перехода на 32-разрядную архитектуру при модернизации своих разработок.

В.Пономарев

Статья опубликована в журнале "ЭЛЕКТРОНИКА: Наука, технология, бизнес" №6 2007 г.

|