AT45DB642

DataFlash память с напряжением питания 2,7 В и двойным интерфейсом

Особенности.

- Питание – однополярное, напряжением от 2.7 до 3.6 В.

Наличие двух интерфейсов:

Специализированный последовательный интерфейс (совместим с SPI Mode 0 и 3)

Специализированный параллельный интерфейс

- Страничные операции программирования:

Перепрограммирование за 1 цикл

8192 страницы (1056 байт/стр.) основной памяти

- Операции очистки страницы и блока

- Два буфера памяти SDRAM объемом по 1056 байт позволяют считывать данные во время перепрограммирования энергонезависимой памяти

- Возможность непрерывного чтения данных по всей матрице

- Малая потребляемая мощность – 4 мА в активном режиме при чтении, 2 мкА в режиме ожидания (standby)

- Максимальная тактовая частота последовательного интерфейса – 20 МГц, параллельного интерфейса – 5 МГц

- Типовое время программирования одной страницы 1.5 мс

- Возможность аппаратной защиты данных

- Выходы и входы совместимы с TTL и CMOS логикой

- Существуют исполнения для коммерческого (0...70°С) и промышленного (-40...85°С) диапазонов температур.

Краткое описание.

AT45DB642 это микросхема Flash памяти с однополярным питанием напряжением 2.7В и двумя интерфейсами обмена данными, пригодная для перепрограммирования внутри системы. Два интерфейса при одновременном использовании позволяют подсоединить к AT45DB642 через последовательный интерфейс к DSP, а через параллельный – микроконтроллер или наоборот. 69’206’016 бит памяти организованы как 8192 страницы по 1056 бит каждая. В дополнение к основной памяти имеются 2 буфера SDRAM емкостью 1056 бит каждый. Буферы позволяют считывать данные во время записи страницы основной памяти. В отличие от обычных микросхем Flash памяти, в которых доступ осуществляется произвольно к каждой ячейке с использованием сложных адресов и параллельного интерфейса, технология DataFlash® использует как последовательный, так и параллельный интерфейс для последовательного доступа к данным, что упрощает топологию кристалла, увеличивает надежность, минимизирует шумы переключения, а также снижает размеры корпуса и необходимое число выводов. Микросхема оптимизирована для широкого круга коммерческих приложений, где необходимы высокая плотность монтажа, малое число выводов, малое напряжение питания, и низкая потребляемая мощность. Диапазон рабочих частот микросхемы – до 20 МГц, при типичном потребляемом токе 4 мА.

Расположение выводов на корпусе микросхемы представлено на рис. 1, назначение выводов описано ниже

| Вывод |

Функция |

| #CS |

Выбор кристалла |

| SCK/CLK |

Вход тактовых импульсов |

| SI |

Последовательный ввод данных |

| SO |

Последовательный вывод данных |

| I/O7 - I/O0 |

Ввод/вывод параллельного интерфейса |

| #WP |

Аппаратная защита страницы от записи |

| #RESET |

Сброс кристалла |

| RDY/#BUSY |

Готов/занят |

| SER/#PAR |

Последовательный/параллельный интерфейс |

Для обеспечения простоты записи микросхема требует напряжения питания 2.7-3.6В как для операции считывания, так и записи. Выбор микросхемы осуществляется подачей на вывод #CS низкого логического уровня, после чего доступ к памяти осуществляется по последовательному трехпроводному интерфейсу (SI –вход, SO - выход, SCK/CLK – тактовые импульсы) или параллельному интерфейсу (I/O0-I/O7 – данные, SCK/CLK – тактовые импульсы).

Все циклы программирования являются самотактируемыми (выполняются встроенным автоматом при внутреннем тактировании), поэтому отдельной операции стирания перед записью не требуется.

В новой микросхеме наиболее значимые страницы массива памяти могут быть не стерты. Другими словами, содержимое последней страницы может быть не заполнено байтами FFh.

Массив памяти

Для достижения наибольшей гибкости массив памяти микросхемы логически разделен на три уровня, включающие сектора, блоки и страницы, что иллюстрирует диаграмма «Архитектура памяти». Все операции чтения/записи производятся только на уровне страниц, но операция стирания может производиться на уровне страницы или блока.

Работа устройства.

Микросхема управляется внешними управляющими командами. Список команд и соответствующих им кодов содержится в таблицах 1 – 4 (приведены в конце инструкции). Инструкция начинается спадом на входе #CS. За ним следует передача 8-ми битового кода операции и необходимого адреса буфера или основной памяти. Пока на входе #CS присутствует низкий уровень, переключение входа SCK/CLK стробирует запись кода операции и адреса буфера или основной памяти в последовательном (SI), либо параллельном (I/O7 - I/O0) формате. При передаче инструкций, адресов и данных первым передается старший бит (MSB). Адрес байта в буфере содержит 11 бит и обозначается в данном руководстве BFA10 - BFA0. Адрес байта в основной памяти состоит из 13-битного адреса страницы (обозначается PA12 - PA0) и 11 битного адреса байта на странице (обозначается BA10 - BA0).

Команды чтения.

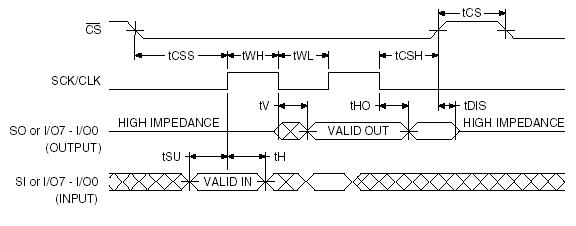

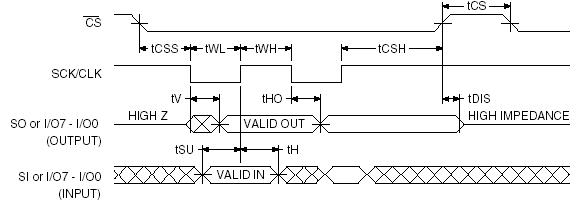

DataFlash поддерживает два класса режимов чтения, в каждом из которых различают два режима. Разница в режимах заключается в неактивном состоянии входа SCK/CLK, а также в том, с какого тактового импульса начинают выдаваться данные. Таким образом, для каждой операции всего имеется 4 режима: неактивное состояние SCK/CLK высокое, неактивное состояние SCK/CLK низкое, SPI Mode 0 и SPI Mode 3. Разным классам операции присвоены разные коды (полный список см. табл. 1). Подробнее с порядком выполнения операций в разных режимах можно ознакомиться по временным диаграммам (обратите внимание, что режим выбирается логическим уровнем на входе SCK/CLK в момент спада на входе #CS и кодом команды).

Непрерывное чтение.

DataFlash включает в себя встроенный адресный счетчик, который может автоматически увеличивать свое значение при приходе очередного тактового импульса. Поэтому, задав начальный стартовый адрес в массиве основной памяти и выдав в микросхему команду непрерывного чтения можно последовательно считывать непрерывным потоком данные, подавая только тактовые импульсы (при этом не требуется никакой дополнительной адресной информации или управляющих сигналов).

Для перехода в режим непрерывного чтения необходимо стробировать в микросхему код команды (68H или E8H), 3 байта адреса (24-битовая последовательность из 13 битного адреса страницы и 11 битного адреса байта на станице) и серию незначащих байт (4 байта при использовании последовательного интерфейса и 60 байт при использовании параллельного). Незначащие байты необходимы только как временная задержка для инициализации операции чтения. После передачи последнего незначащего байта по каждому следующему тактовому импульсу происходит вывод очередной порции данных (на вывод SO или IO7-IO0).

Во время загрузки кода операции, байтов адреса, незначащих байт и чтения данных на входе #CS должен присутствовать низкий логический уровень. Если во время операции достигается конец страницы памяти , чтение продолжается с начала следующей страницы без задержек во время перехода границы страницы. Когда последний бит (или байт, если используется параллельный интерфейс) основной памяти будет прочитан, чтение будет продолжено с начала первой страницы, при этом также не происходит задержки при переходе с конца массива памяти в начало.

По фронту сигнала на входе #CS происходит завершение операции непрерывного чтения и переход выходов (SO или IO7-IO0) в высокоимпедансное состояние. Максимальная тактовая частота, при которой возможна операция непрерывного чтения, определена в спецификации как fCAR. Операция не использует буферы, и оставляет их содержимое в неизменном состоянии.

Пакетное чтение с синхронной задержкой.

Пакетное чтение с синхронной задержкой очень схоже с непрерывным чтением, но поддерживает более высокие скорости вывода, используя более высокие тактовые частоты. В этом режиме при переходе границ страницы происходит задержка в выдаче данных, при которой на несколько тактовых импульсов выдаются незначащие байты. Для выполнения этой операции надо стробировать в микросхему команду пакетного чтения (69H или E9H ), начальный стартовый адрес в массиве основной памяти (24-битовая последовательность из 13 битного адреса страницы и 11 битного адреса байта на станице) и серию незначащих байт (4 байта при использовании последовательного интерфейса и 60 байт при использовании параллельного). Незначащие байты необходимы только как временная задержка для инициализации операции чтения. После передачи последнего незначащего байта по каждому следующему тактовому импульсу происходит вывод данных из микросхемы (на вывод SO или IO7-IO0).

На входе #CS должен присутствовать низкий логический уровень во время загрузки кода операции, байтов адреса, незначащих байт и чтения данных. Если во время операции пакетного чтения достигается конец страницы памяти (выведен последний бит или байт страницы), чтение продолжается с начала следующей страницы с задержкой в 32 тактовых импульса во время перехода границы страницы. Более подробно это проиллюстрировано в разделе «Временные диаграммы».

Когда последний бит (или байт при использовании параллельного интерфейса) основной памяти прочитан, чтение продолжается с начала первой страницы памяти. Переход с конца массива памяти в начало также сопровождается задержкой в 32 тактовых импульса.

По фронту сигнала #CS прекращается операция чтения и выходы (SO и I/O7-I/O0) переводятся в высокоимпедансное состояние. Максимальное значение тактовой частоты для этого режима указано в спецификации как fBARSD. Операция не использует буферы и не изменяет содержимое буферов.

Постраничное чтение основной памяти.

Этот режим позволяет считывать данные с любой одной страницы из 8192 страниц основной памяти, не используя буферы, и не изменяя содержимое буферов. Для начала чтения страницы необходимо задать код операции 52H или D2H , 3 байта адреса (24-битовая последовательность из 13-битного адреса страницы и 11-битного адреса байта на станице) и серию незначащих байт (4 байта при использовании последовательного интерфейса и 60 байт при использовании параллельного). Незначащие байты необходимы только как временная задержка для инициализации операции чтения. После передачи последнего незначащего байта по каждому следующему тактовому импульсу происходит вывод данных их микросхемы (на вывод SO или I/O7-I/O0). Во время загрузки кода операции, байтов адреса, незначащих байт и чтения данных на входе #CS должен присутствовать низкий логический уровень.

При достижении конца страницы чтение продолжается с начала той же страницы. Фронт сигнала на входе #CS прекращает операцию чтения и переводит выходы (SO и I/O7-I/O0) в высокоимпедансное состояние.

Чтение буфера

Данные могут считываться из любого из двух буферов, при этом каждому буферу присвоен свой код операции чтения (54H или D4H - для буфера 1, 56H или D6H - для буфера 2). Для начала чтения содержимого буфера необходимо стробировать в микросхему код операции (54H или D4H для чтения буфера 1, 56H или D6H для чтения буфера 2), 3 байта адреса (24 битная последовательность из 13 незначащий бит и 11 бит адреса бита в буфере) и серию незначащих байт. Во время загрузки кода операции, байтов адреса, незначащих байт и чтения данных на входе #CS должен присутствовать низкий логический уровень. При достижении конца буфера чтение продолжается с начала буфера. Фронт сигнала на входе #CS прекращает операцию чтения и переводит выходы (SO и I/O7-I/O0) в высокоимпедансное состояние.

Чтение регистра состояния.

Анализируя содержимое регистра состояния можно определить готовность (неготовность) устройства, результаты сравнения содержимого страниц памяти или буферов, и емкость микросхемы. Для начала чтения содержимого регистра состояния необходимо выдать в микросхему код операции (57H или D7H). Со следующего тактового импульса после передачи кода операции микросхема выводит 1 байт содержимого регистра состояния (при использовании последовательного интерфейса данные выводятся начиная со старшего бита в течение 8 тактовых циклов).

Старшие пять бит регистра состояния содержат информацию об устройстве, младшие три в настоящее время не используются и могут содержать любые значения. После выдачи восьми бит регистра статуса последовательность повторяется до тех пор, пока на входе #CS низкий логический уровень и присутствуют тактовые импульсы на входе SCK/CLK. Данные в регистре состояния постоянно обновляются, при повторении последовательности выдаются обновленные данные.

Состояние готовности устройства определяется содержимым 7 бита регистра состояния. Если этот бит 1, то устройство не занято, если 0, то устройство занято. Постоянный опрос 7 бита регистра состояния можно получить, зафиксировав низкий логический уровень на входе SCK/CLK, как только этот бит выдан на вывод SO или IO7. Состояние 7 бита будет продолжать выводиться на вывод SO или IO7, и, как только устройство освободится, состояние вывода SO или IO7 изменится на противоположное (из 0 в 1). Устройство может находиться в занятом состоянии при выполнении следующих 8 операций: передачи содержимого страницы памяти в буфер, сравнения содержимого страницы памяти и буфера, передачи содержимого буфера на страницу памяти со встроенным стиранием, передачи содержимого буфера на страницу памяти без встроенного стирания, стирания страницы, стирания блока, записи на страницу, автоматической переписи страницы.

Результат последней операции сравнения содержимого страницы памяти и буфера содержится в 6 бите регистра состояния. Если этот бит установлен в 0, то содержимое полностью совпадает, в 1 - хотя бы 1 бит содержимого страницы памяти и буфера не совпадает.

Емкость устройства определяется битами 5, 4 и 3 регистра состояния, в которых записан код, соответствующий различным емкостям устройств DataFlash. Для AT45DB642 эти три бита – 1,1,1.

Формат регистра состояния.

| Бит 7 |

Бит 6 |

Бит 5 |

Бит 4 |

Бит 3 |

Бит 2 |

Бит 1 |

Бит 0 |

| RDY/#BUSY |

Comp |

1 |

1 |

1 |

x |

x |

x |

0 - готов

1 - занят |

0 – совпадает

1 – не совпадает |

код 0 1 0 - объем прибора 2 Мбит

код 0 1 1 - объем прибора 4 Мбит

код 1 0 0 - объем прибора 8 Мбит

…

код 1 1 1 - объем прибора 64 Мбит

X - состояние значения не имеет - зарезервированные биты. |

Команды стирания и записи.

Запись в буфер.

Данные могут записываться в любой из двух буферов. Для записи данных требуется выдать однобайтовую команду (84H для буфера 1 или 87H для буфера 2), затем три байта адреса (13 незначащих бит и 11 бит с адресом байта в буфере BFA10- BFA0). После записи последнего байта адреса со следующего тактового импульса можно выдавать данные для записи в буфер. При достижении конца буфера данные продолжают записываться с начала буфера, что будет продолжаться до фронта сигнала на входе #CS.

Копирование содержимого буфера в основную память со встроенным стиранием.

Данные, записанные в любой из буферов можно скопировать в основную память. Время копирования зависит от используемой команды (нормальный или ускоренный режим, в котором потребляется большая мощность). Формат команды: однобайтный код команды (83H для буфера 1 и 86H для буфера 2 при использовании обычного режима или 93H для буфера 1 и 96H для буфера 2 при использовании ускоренного режима), три байта адреса (13 бит адреса страницы и 11 незначащих бит). По фронту сигнала на входе #CS сначала происходит стирание выбранной страницы (стертое состояние бита - 1), затем происходит запись данных из буфера на выбранную страницу памяти. Как стирание, так и запись тактируются внутренним автоматом и требуют максимального времени tEP для нормальной записи и tFEP для ускоренной записи. Во время выполнения этой операции 7ой бит регистра состояния и вывод RDY/#BUSY устанавливаются в состояние, соответствующее неготовности устройства.

Копирование содержимого буфера в основную память без встроенного стирания.

На предварительно стертую страницу памяти можно скопировать данные из любого буфера. Время копирования зависит от используемой команды (нормальный или ускоренный режим, в котором потребляется большая мощность). Формат команды: однобайтный код команды (88H для буфера 1 и 89H для буфера 2 при использовании обычного режима или 98H для буфера 1 и 99H для буфера 2 при использовании ускоренного режима), три байта адреса (13 бит адреса страницы и 11 незначащих бит). По фронту сигнала на входе #CS происходит запись данных из буфера на выбранную страницу памяти. При этом необходимо, чтобы страница, на которую происходит запись, предварительно была стерта. Операция записи самотактируемая, требует максимального времени tP для нормальной записи и tFP для ускоренной записи. Во время выполнения этой операции 7ой бит регистра состояния и вывод RDY/#BUSY устанавливаются в состояние, соответствующее неготовности устройства.

Последовательные записи на страницу без стирания не рекомендуются. Другими словами, не рекомендуется изменение бита из 1 в 0 при нескольких операциях записи на страницу без её предварительного стирания.

Стирание страницы.

Команда очистки содержимого страницы памяти используется для стирания содержимого любой страницы, с возможностью последующей переноса содержимого буфера на страницу без встроенного стирания. Формат команды: код операции (81H), 3 байта адреса (13 бит адреса стираемой страницы бит и 11 незначащих бит). По фронту сигнала на входе #CS происходит стирание выбранной страницы памяти (стертое состояние бита - 1). Операция самотактируемая, занимает время не более tPE. Во время выполнения этой операции 7ой бит регистра состояния и вывод RDY/#BUSY устанавливаются в состояние, соответствующее неготовности устройства.

Стирание блока.

Блок из восьми страниц может быть стерт одновременно, что позволяет применять команду переноса из буфера в память без стирания для уменьшения времени записи при записи больших блоков данных. Для стирания блока необходимо выдать код операции 50H и три байта адреса (10 бит адреса стираемого блока и 14 незначащих бит). По фронту сигнала на входе #CS происходит стирание содержимого блока. Операция самотактируемая, занимает время не более tBE. Во время стирания 7ой бит регистра состояния и вывод RDY/#BUSY устанавливаются в состояние, соответствующее неготовности устройства.

Задание адреса стираемого блока

| PA12 |

PA11 |

PA10 |

PA 9 |

PA8 |

PA7 |

PA6 |

PA5 |

PA4 |

PA3 |

PA2 |

PA1 |

PA0 |

Блок |

| 0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

X |

X |

X |

0 |

| 0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

X |

X |

X |

1 |

| 0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

X |

X |

X |

2 |

| ... |

... |

... |

... |

... |

... |

... |

... |

... |

... |

X |

X |

X |

... |

| 1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

X |

X |

X |

1022 |

| 1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

X |

X |

X |

1023 |

Запись в основную память через буфер.

Эта операция является комбинацией записи в буфер и переноса из буфера в основную память со встроенным стиранием. Данные сначала записываются в буфер, а потом переписываются на указанную страницу основной памяти. Время записи зависит от используемого режима записи (нормальный или быстрый режим, в котором потребляется большая мощность). Формат команды: однобайтный код команды (82H для буфера 1 и 85H для буфера 2 при использовании обычного режима или 92H для буфера 1 и 95H для буфера 2 при использовании ускоренного режима), три байта адреса (13 бит адреса страницы и 11 бит адреса бита в буфере, с которого начинается запись в буфер). После передачи команды и адресных бит микросхема начинает принимать данные со входов и записывать их в указанном буфере. Если происходит достижение конца буфера, то запись продолжается с начала буфера. По фронтe на входе #CS происходит стирание выбранной страницы памяти и копирование содержимого буфера на стертую страницу. Как стирание, так и копирование самотактируемые и занимают не более tEP для нормального режима и tFEP для быстрого режима. Во время выполнения этой операции 7ой бит регистра состояния и вывод RDY/#BUSY устанавливаются в состояние, соответствующее неготовности устройства.

Дополнительные операции.

Копирование из основной памяти в буфер.

Содержимое страницы памяти может быть переписано в любой из двух буферов. Для выполнения этой операции надо стробировать в микросхему 1 байт кода операции (53H для буфера 1 или 55H для буфера 2) и три байта адреса (13 бит адреса переписываемой страницы и 11 незначащих бит). Во время передачи кода операции и байт адреса на входе #CS должен присутствовать низкий логический уровень. Передача содержимого страницы начинается по фронту на входе #CS. Во время операции переноса (не более tXFR) можно отслеживать регистр состояния для определения момента окончания операции.

Сравнение содержимого страницы и буфера

Содержимое страницы памяти можно сравнить с содержимым любого из буферов. Для выполнения этой операции надо выдать в микросхему 1 байт кода операции (60H для буфера 1 или 61H для буфера 2) и три байта адреса (13 бит адреса сравниваемой страницы и 11 незначащих бит). Во время передачи кода операции и байт адреса на входе #CS должен присутствовать низкий логический уровень. С возрастающего фронта на входе #CS начинается сравнение 1056 байт содержимого страницы с 1056 байтами содержимого буфера. Во время операции переноса (не более tXFR) 7ой бит регистра состояния и вывод RDY/#BUSY устанавливаются в состояние, соответствующее неготовности устройства. После окончания по результатам операции сравнения обновляется содержимое 6го бита регистра состояния.

Автоматическая перезапись страницы через буфер

Эта операция применяется в том случае, когда несколько байтов страницы или несколько страниц данных были перепрограммированы в произвольном порядке. Является комбинацией двух операций: переноса содержимого страницы в буфер и копирования буфера в память со встроенным стиранием. При этом содержимое страницы сначала копируется в буфер 1 или 2, а затем те же самые данные копируются обратно на страницу. Для выполнения этой операции надо выдать в микросхему 1 байт кода операции (58H для буфера 1 или 59H для буфера 2) и три байта адреса (13 бит адреса страницы и 11 незначащих бит). Операция начинается с приходом возрастающего фронта на вход #CS. Во время операции (не более tEP) 7ой бит регистра состояния и вывод RDY/#BUSY устанавливаются в состояние, соответствующее неготовности устройства.

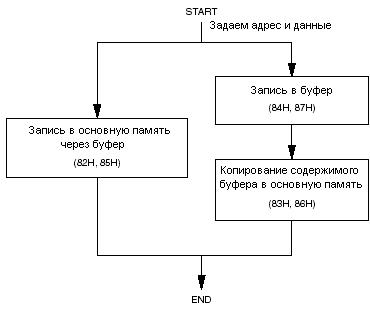

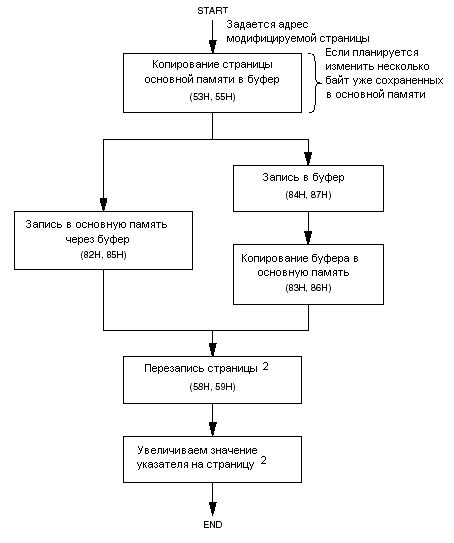

При записи сектора последовательно страница за страницей, то рекомендуется алгоритм, показанный на рис. 1. В случае, когда много записываемых байт на странице или несколько записываемых страниц в секторе расположены случайным образом, рекомендуется алгоритм, показанный на рис. 2.

Резюме.

Описанные операции можно разделить на 2 группы: операции, использующие основную Flash память, и операции, не использующие ее.

Используют основную Flash память:

- Копирование содержимого страницы памяти в буфер

- Сравнение содержимого страницы памяти и буфер

- Копирование содержимого буфера на страницу памяти с встроенным стиранием

- Копирование содержимого буфера на страницу памяти без встроенного стирания

- Стирание страницы

- Стирание блока

- Запись на страницу памяти с использованием буфера

- Автоматическая перезапись страницы

Не используют основную Flash память:

- Чтение из буфера

- Запись в буфер

- Чтение регистра состояния

Если одна из операций первой группы выполняется (еще не завершена), то другая операция из той же группы не может быть запущена. Однако, в это время возможен запуск операций второй группы. Это дает возможность виртуально записывать непрерывный поток данных. Пока данные переносятся из буфера 1 можно записывать данные в буфер 2 и наоборот. Рекомендуем ознакомиться с инструкцией по применению AN-4 (“Using Atmel’s Serial DataFlash”).

Описание выводов.

SER/#PAR. Выбор используемого интерфейса. Если на данном входе удерживается высокий логический уровень, то для ввода/вывода используется последовательный интерфейс (SI, SO), при этом выводы параллельного интерфейса (IO7-IO0) находятся в высокоимпедансном состоянии и данные на них игнорируются. Если на данном входе удерживается низкий логический уровень, то для ввода/вывода используется параллельный интерфейс (IO7-IO0), вывод SO находится в высокоимпедансном состоянии, а данные на входе SI игнорируются.

Переключение используемого интерфейса может происходить в любое время при удовлетворении следующих условий:

- На входе #CS должен удерживаться высокий логический уровень в течение всего времени переключения

- Должны выполняться требования по TSPH (времени удержания SER/#PAR) и TSPS (времени установления SER/#PAR).

Наличие двух интерфейсов позволяет подключать микросхему к 2м шинам, которые могут быть подключены к разным контроллерам. Преимущество переключения между режимами состоит в том, что в то время как одна из самосинхронизируемых операций (например, стирание) запущена на выполнение с использованием одного порта, операции чтения и записи могут выполняться и использованием другого порта.

Вывод SER/#PAR имеет внутренний подтягивающий резистор, поэтому, если Вы вообще не используете параллельный интерфейс, этот вывод можно не подключать. Кроме того, если ввод SER/#PAR не подключен или на нем удерживается высокий логический уровень то выводы ввода/вывода параллельного интерфейса (IO7-IO0), вывод VCCP и GNDP будут обрабатываться как «не подключенные».

SI. Вход последовательного интерфейса. Этот вывод используется только для побитового ввода данных (в том числе кодов операций и адресов) при использовании последовательного интерфейса. Если на вводе SER/#PAR присутствует низкий логический уровень, то этот вывод обрабатывается как «не подключенный».

SO. Выход последовательного интерфейса. Этот вывод используется только для побитового вывода данных при использовании последовательного интерфейса. Если на вводе SER/#PAR присутствует низкий логический уровень, то этот вывод обрабатывается как «не подключенный».

I/O7-I/O0. Выводы параллельного ввода/вывода. Эти выводы используется для побайтового ввода/вывода данных при использовании параллельного интерфейса. Если на вводе SER/#PAR присутствует высокий логический уровень или он не подключен, то эти выводы обрабатываются как «не подключенные».

SCK/CLK. Вход тактовых импульсов. Используется для тактирования потока данных. Данные считываются в микросхему по фронту тактовых импульсов, а выводятся из микросхемы по спаду тактовых импульсов.

#CS. Вход выбора кристалла. Выбор кристалла осуществляется подачей низкого логического уровня на этот вход. Когда кристалл не выбран не осуществляется считывание данных со входов данных (SI и IO7-IO0) в микросхему, а выходы данных (SO и IO7-IO0) находятся в высокоимпедансном состоянии.

#WP. Это вход аппаратной защиты от записи. Когда на этом входе присутствует низкий логический уровень первые 256 страниц (сектора 0 и 1) основной памяти не могут быть перепрограммированы. При этом единственным способом перепрограммирования указанных областей является предварительная установка на входе #WP высокого логического уровня и последующее стирание. Данный вход имеет внутренний подтягивающий резистор, поэтому подключение этого входа не обязательно (если функция аппаратной защиты не используется), однако рекомендуется задавать высокий логический уровень на этом входе извне во всех случаях, когда это возможно.

#RESET. Вход сигнала сброса. Появление низкого логического уровня на этом входе прекращает выполняемую операцию и переводит внутреннюю схему управления в неактивное состояние. Микросхема находится в состоянии сброса в течение всего времени, пока на входе #RESET удерживается низкий логический уровень. Нормальное функционирование восстанавливается только после установления на этом входе высокого логического уровня.

Микросхема включает в себя встроенную схемы сброса по включению питания, поэтому никаких ограничений на состояние входа #RESET во время включения питания не накладывается. Вход #RESET имеет внутренний подтягивающий резистор, поэтому подключение этого входа не обязательно (если функция внешнего сброса не используется), однако рекомендуется задавать высокий логический уровень на этом входе извне во всех случаях, когда это возможно.

READ/#BUSY. На этом выводе с открытым стоком будет присутствовать низкий логический уровень, если устройство выполняет одну из самотактируемых операций. Высокий логический уровень (при использовании внешнего подтягивающего резистора) сменяется низким при выполнении операций записи, стирания, сравнения и переноса.

Состояние неготовности сигнализирует о том, что в настоящий момент доступ к массиву основной памяти и одному из буферов отсутствует, при этом могут производиться операции чтения/записи с другим буфером.

VCCP и GNDP. Выводы для подачи напряжения питания для параллельного интерфейса (IO7-IO0). Эти выводы должны быть подключены, если предполагается использование последовательного интерфейса. Однако если на входе SER/#PAR присутствует высокий логический уровень или он не подключен, то эти выводы обрабатываются как «не подключенные»

Сброс при включении питания

При включении питания или после сброса микросхема по умолчанию находится в режиме SPI 3 или высокий неактивный тактовый уровень. Кроме того, выводы SO и I/O7-I/O0 находятся в высокоимпедансном состоянии и для запуска на выполнение команды требуется спадающий фронт на входе #CS. Режим SPI или неактивный тактовый уровень будет автоматически выбран по спаду на входе #CS путем замера логического уровня на входе SCK/CLK.

Табл. 1 Команды чтения.

| Операция |

Режим SCK/CLK |

Код операции |

| Непрерывное чтение. |

Неактивное состояние такта низкое или высокое |

68H |

| SPI Mode 0 или 3 |

E8H |

| Пакетное чтение с синхронной задержкой |

Неактивное состояние такта низкое или высокое |

69H |

| SPI Mode 0 или 3 |

E9H |

| Чтение страницы памяти |

Неактивное состояние такта низкое или высокое |

52H |

| SPI Mode 0 или 3 |

D2H |

| Чтение буфера 1 |

Неактивное состояние такта низкое или высокое |

54H |

| SPI Mode 0 или 3 |

E4H |

| Чтение буфера 2 |

Неактивное состояние такта низкое или высокое |

56H |

| SPI Mode 0 или 3 |

E6H |

| Чтение регистра состояния |

Неактивное состояние такта низкое или высокое |

57H |

| SPI Mode 0 или 3 |

E7H |

Табл. 2 Команды записи и стирания.

| Операция |

Режим SCK/CLK |

Код операции |

| Запись в буфер 1 |

Любой |

84H |

| Запись в буфер 2 |

Любой |

87H |

| Копирование буфера 1 в основную память со встроенным стиранием |

Любой |

83H |

| Копирование буфера 1 в основную память со встроенным стиранием (ускор.) |

Любой |

93H |

| Копирование буфера 2 в основную память со встроенным стиранием |

Любой |

86H |

| Копирование буфера 2 в основную память со встроенным стиранием (ускор.) |

Любой |

96H |

| Копирование буфера 1 в основную память без встроенным стиранием |

Любой |

88H |

| Копирование буфера 1 в основную память без встроенным стиранием (ускор.) |

Любой |

98H |

| Копирование буфера 2 в основную память без встроенным стиранием |

Любой |

89H |

| Копирование буфера 2 в основную память без встроенным стиранием (ускор.) |

Любой |

99H |

| Стирание страницы |

Любой |

81H |

| Стирание блока |

Любой |

50H |

| Запись в память через буфер 1 |

Любой |

82H |

| Запись в память через буфер 1 (ускор.) |

Любой |

92H |

| Запись в память через буфер 2 |

Любой |

85H |

| Запись в память через буфер 2 (ускор.) |

Любой |

95H |

Табл. 3 Дополнительные команды

| Операция |

Режим SCK/CLK |

Код операции |

| Копирование страницы памяти в буфер 1 |

Любой |

53H |

| Копирование страницы памяти в буфер 2 |

Любой |

55H |

| Сравнение содержимого страницы с содержимым буфера 1 |

Любой |

60H |

| Сравнение содержимого страницы с содержимым буфера 2 |

Любой |

61H |

| Автоматическая перепись страницы с использованием буфера 1 |

Любой |

58H |

| Автоматическая перепись страницы с использованием буфера 2 |

Любой |

59H |

Примечание: в таблицах 2 и 3 значение «Любой» в графе «режим SCK/CLK» означает любой из четырех возможных режимов: неактивное состояние SCK/CLK низкое, неактивное состояние SCK/CLK высокое,SPI Mode 0 и SPI Mode 3.

Табл. 4 Детальная структура команд

| Код |

Код |

Байт адреса |

Байт адреса |

Байт адреса |

Доп. незнач. биты |

| PA12 |

PA11 |

PA10 |

PA9 |

PA8 |

PA7 |

PA6 |

PA5 |

PA4 |

PA3 |

PA2 |

PA1 |

PA0 |

BA10 |

BA9 |

BA8 |

BA7 |

BA6 |

BA5 |

BA4 |

BA3 |

BA2 |

BA1 |

BA0 |

| 50H |

01010000 |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

N/A |

| 52H |

01010010 |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

B |

B |

B |

B |

B |

B |

B |

B |

B |

B |

B |

4 (60*) байт |

| 53H |

01010011 |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

N/A |

| 54H |

01010100 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

B |

B |

B |

B |

B |

B |

B |

B |

B |

B |

B |

1 байт |

| 55H |

01010101 |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

N/A |

| 56H |

01010110 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

B |

B |

B |

B |

B |

B |

B |

B |

B |

B |

B |

1 байт |

| 57H |

01010111 |

N/A |

N/A |

N/A |

N/A |

| 58H |

01011000 |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

N/A |

| 59H |

01011001 |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

N/A |

| 60H |

01100000 |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

N/A |

| 61H |

01100001 |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

N/A |

| 68H |

01101000 |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

B |

B |

B |

B |

B |

B |

B |

B |

B |

B |

B |

4 (60*) байт |

| 69H |

01101001 |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

B |

B |

B |

B |

B |

B |

B |

B |

B |

B |

B |

4 (60*) байт |

| 81H |

10000001 |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

N/A |

| 82H |

10000010 |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

B |

B |

B |

B |

B |

B |

B |

B |

B |

B |

B |

N/A |

| 83H |

10000011 |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

N/A |

| 84H |

10000100 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

B |

B |

B |

B |

B |

B |

B |

B |

B |

B |

B |

N/A |

| 85H |

10000101 |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

B |

B |

B |

B |

B |

B |

B |

B |

B |

B |

B |

N/A |

| 86H |

10000110 |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

N/A |

| 87H |

10000111 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

B |

B |

B |

B |

B |

B |

B |

B |

B |

B |

B |

N/A |

| 88H |

10001000 |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

N/A |

| 89H |

10001001 |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

N/A |

| 92H |

10010010 |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

B |

B |

B |

B |

B |

B |

B |

B |

B |

B |

B |

N/A |

| 93H |

10010011 |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

N/A |

| 95H |

10010101 |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

B |

B |

B |

B |

B |

B |

B |

B |

B |

B |

B |

N/A |

| 96H |

10010110 |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

N/A |

| 98H |

10011000 |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

N/A |

| 99H |

10011001 |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

N/A |

| D2H |

11010010 |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

B |

B |

B |

B |

B |

B |

B |

B |

B |

B |

B |

4 (60*) байт |

| D4H |

11010100 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

B |

B |

B |

B |

B |

B |

B |

B |

B |

B |

B |

1 байт |

| D6H |

11010110 |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

x |

B |

B |

B |

B |

B |

B |

B |

B |

B |

B |

B |

1 байт |

| D7H |

11010111 |

N/A |

N/A |

N/A |

N/A |

| E8H |

11101000 |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

B |

B |

B |

B |

B |

B |

B |

B |

B |

B |

B |

4 (60*) байт |

| E9H |

11101001 |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

P |

B |

B |

B |

B |

B |

B |

B |

B |

B |

B |

B |

4 (60*) байт |

N/A – не требуется

P – бит адреса страницы

B – бит адреса на странице или в буфере

x – незначащий бит

* 4 байта для последовательного ввода и 60 для параллельного

Максимально допустимые параметры.

| Рабочая температура |

-55°С.. +125°С |

| Температура хранения |

-65°С.. +150°С |

| Все входные напряжения (в том числе на NC выводах) по отношению к "земле". |

-0.6В.. 6.25В |

| Все выходные по отношению к «земле» |

-0.6В..VCC+0.6В |

Выход параметров за пределы, указанные таблице, может привести к нарушению работоспособности микросхемы. Это только предельные значение параметров, рабочие значения приведены ниже. Удержание предельных значений на выводах микросхемы в течение длительного времени может привести к потере работоспособности микросхемы.

Параметры по переменному и постоянному току.

| Параметр |

Исполнение |

AT45DB642 |

| Рабочая температура корпуса |

Коммерческое |

0°С.. 70°С |

| Промышленное |

-40°С..+85°С |

| Напряжение питания (1) VCC |

|

2.7В..3.6В |

1 - После подачи напряжения питания, большего минимального значения, микросхема ожидает 20 мс до начала функционирования.

Параметры по постоянному току.

| Обозн. |

Параметр |

Условия |

Мин. |

Тип. |

Макс. |

Ед. |

| Isb |

Потребляемый ток в режиме ожидания |

#CS, #RESET, #WP - VIH, на всех входах CMOS логические уровни |

|

2 |

10 |

мкА |

| ICC1(1) |

Потребляемый ток в режиме чтения (посл. интерфейс) |

f = 20 MHz; IOUT = 0 мА; VCC = 3.6 В |

|

4 |

10 |

мА |

| ICC2(2) |

Потребляемый ток в режиме чтения (паралл. интерфейс) |

f= 5 МГц; IOUT= 0 мА ; VCC = 3.6 В |

|

8 |

15 |

мА |

| ICC3 |

Потребляемый ток в режиме записи на страницу |

VCC = 3.6 В |

|

20 |

35 |

мА |

| ICC4 |

Потребляемый ток в режиме ускоренной записи на страницу |

VCC = 3.6 В |

|

30 |

50 |

мА |

| ICC5 |

Потребляемый ток в режиме стирания страницы |

VCC = 3.6 В |

|

20 |

35 |

мА |

| ICC6 |

Потребляемый ток в режиме стирания блока |

VCC = 3.6 В |

|

20 |

35 |

мА |

| ILI |

Входной втекающий ток |

VIN = CMOS лог. уровням |

|

|

1 |

мкА |

| ILO |

Выходной вытекающий ток |

VI/O = CMOS лог. уровням |

|

|

1 |

мкА |

| VIL |

Входное напряжение низкого лог. уровня |

|

|

|

0.6 |

В |

| VIH |

Входное напряжение высокого лог. уровня |

|

2.0 |

|

|

В |

| VOL |

Выходное напряжение низкого лог. уровня |

IOL = 1.6 мА; VCC = 2.7 В |

|

|

0.4 |

В |

| VOH |

Выходное напряжение высокого лог. уровня |

IOH= -100мкА |

VСС - 0.2V |

|

|

В |

Примечания:

1.Максимальное значение ICC1 во время чтения буфера 20 мА.

2.Максимальное значение ICC2 во время чтения буфера 25 мА.

Параметры по переменному току.

| Обозн. |

Параметр |

Мин. |

Макс. |

Ед. |

| tSPH |

Время удержания вывода SER/#PAR |

100 |

|

нс |

| tSPS |

Время установления вывода SER/#PAR |

100 |

|

нс |

Характеристики по переменному току. Последовательный интерфейс.

| Обозначение |

Параметр |

Мин. |

Макс. |

Ед. |

| fSCK |

Частота тактовых импульсов |

|

20 |

МГц |

| fCAR |

Частота тактовых импульсов для непрерывного чтения |

|

15 |

МГц |

| fBARSD |

Частота тактовых импульсов для чтения блоками |

|

20 |

МГц |

| tWH |

Высокий логический уровень тактового импульса |

22 |

|

нс |

| tWL |

Низкий логический уровень тактового импульса |

22 |

|

нс |

| t#CS |

Мин. время присутствия высокого лог. уровня на входе #CS |

250 |

|

нс |

| t#CSS |

Время установления #CS |

250 |

|

нс |

| t#CSH |

Время удержания #CS |

250 |

|

нс |

| t#CSB |

Время между установлением #CS в "1" и установлением RDY/#BUSY в "0" |

|

150 |

нс |

| tSU |

Время установления входных данных |

5 |

|

нс |

| tH |

Время удержания входных данных |

10 |

|

нс |

| tHO |

Время удержания выходных данных |

0 |

|

нс |

| tDIS |

Время отключения выходов |

|

18 |

нс |

| tV |

Время корректности выходных данных |

|

20 |

нс |

| tXFR |

Время копирования/сравнения буфера и страницы |

|

700 |

мкс |

| tEP |

Время очистки и записи страницы |

|

20 |

мс |

| tP |

Время записи страницы |

|

14 |

мс |

| tFEP |

Время очистки и записи страницы в ускоренном режиме1 |

|

10 |

мс |

| tFP |

Время записи страницы в ускоренном режиме1 |

|

2 |

мс |

| tPE |

Время очистки страницы |

|

8 |

мс |

| tBE |

Время очистки блока |

|

12 |

мс |

| tRST |

Длительность импульса #RESET |

10 |

|

мкс |

| tREC |

Время восстановления входа #RESET |

|

1 |

мкс |

1.Для приложений, требующих длительных записей, рекомендуется использовать стандартное время программирования.

Характеристики по переменному току. Параллельный интерфейс.

| Обозначение |

Параметр |

Мин. |

Макс. |

Ед. |

| fSCK1 |

Частота тактовых импульсов |

|

5 |

МГц |

| fCAR1 |

Частота тактовых импульсов для непрерывного чтения |

|

3 |

МГц |

| fBARSD1 |

Частота тактовых импульсов для чтения блоками |

|

5 |

МГц |

| tWH |

Высокий логический уровень тактового импульса |

80 |

|

нс |

| tWL |

Низкий логический уровень тактового импульса |

80 |

|

нс |

| t#CS |

Мин. время присутствия высокого лог. уровня на входе #CS |

250 |

|

нс |

| t#CSS |

Время установления #CS |

250 |

|

нс |

| t#CSH |

Время удержания #CS |

250 |

|

нс |

| t#CSB |

Время между установлением #CS в ‘1’ и установлением RDY/#BUSY в ‘0’ |

|

150 |

нс |

| tSU |

Время установления входных данных |

75 |

|

нс |

| tH |

Время удержания входных данных |

25 |

|

нс |

| tHO |

Время удержания выходных данных |

0 |

|

нс |

| tDIS |

Время отключения выходов |

|

55 |

нс |

| tV |

Время корректности выходных данных |

|

70 |

нс |

| tXFR |

Время копирования/сравнения буфера и страницы |

|

700 |

мкс |

| tEP |

Время очистки и записи страницы |

|

20 |

мс |

| tP |

Время записи страницы |

|

14 |

мс |

| tFEP |

Время очистки и записи страницы в ускоренном режиме |

|

10 |

мс |

| tFP |

Время записи страницы в ускоренном режиме |

|

2 |

мс |

| tPE |

Время очистки страницы |

|

8 |

мс |

| tBE |

Время очистки блока |

|

12 |

мс |

| tRST |

Длительность импульса #RESET |

10 |

|

мкс |

| tREC |

Время восстановления входа #RESET |

|

1 |

мкс |

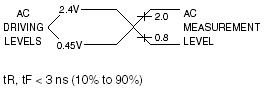

Тестовые сигналы и измеряемые уровни.

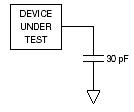

Нагрузка для тестирования выхода.

Временные диаграммы сигналов.

Две различные временные диаграммы приведены ниже. Диаграмма 1 соответствует случаю, когда на входе SCK/CLK присутствует низкий логический уровень во время спада сигнала на входе #CS. Диаграмма 2 соответствует случаю, когда на входе SCK/CLK присутствует высокий логический уровень во время спада сигнала на входе #CS. Обе диаграммы являются правильными временными диаграммами. Времена установления и удержания входных сигналов (SI и I/O7 – I/O0) отсчитываются от фронта сигнала SCK/CLK. Диаграмма 1 показывает временные соотношения, также совместимые с SPI MODE 0, а диаграмма 2 - с SPI Mode 3.

DRAW_8 – DRAW_48 с пояснениями из файла «Список рисунков»

Алгоритм записи последовательные ячейки массива основной памяти.

Прим:

1. Алгоритмы такого типа используются в тех приложениях, где запись в массив основной памяти происходит в последовательно расположенные ячейки, страница за страницей.

2.Страницы могут записываться как напрямую, так и с промежуточной записью в буфер.

3.Показанный алгоритм иллюстрирует запись одной страницы. Для записи нескольких страниц этот алгоритм надо повторить для каждой страницы.

Алгоритм модификации произвольно расположенных данных.

Прим:

Для предотвращения потери данных каждая страница сектора DataFlash должна обновляться/перезаписываться через каждые 10000 операций стирания/записи.

Надо использовать указатель адреса страницы, чтобы отслеживать текущую рабочую страницу. Значение этого указателя надо передавать в команду автоматической перезаписи.

Можно использовать и другие алгоритмы освежения содержимого Flash памяти. В приложениях, критичные к энергопотреблению можно производить перезапись всех страниц сектора только после проведения (в сумме) 10000 операций записи/стирания.

Адресация секторов.

| PA12 |

PA11 |

PA10 |

PA9 |

PA8 |

PA7 |

PA6 |

PA5 |

PA4 |

PA3 |

PA2-PA0 |

Сектор |

| 0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

x |

0 |

| 0 |

0 |

0 |

0 |

0 |

1 |

x |

x |

x |

x |

x |

1 |

| 0 |

0 |

0 |

0 |

1 |

0 |

x |

x |

x |

x |

x |

2 |

| 0 |

0 |

0 |

0 |

1 |

1 |

x |

x |

x |

x |

x |

3 |

| - |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

- |

| 1 |

1 |

1 |

1 |

1 |

0 |

x |

x |

x |

x |

x |

31 |

| 1 |

1 |

1 |

1 |

1 |

1 |

x |

x |

x |

x |

x |

32 |

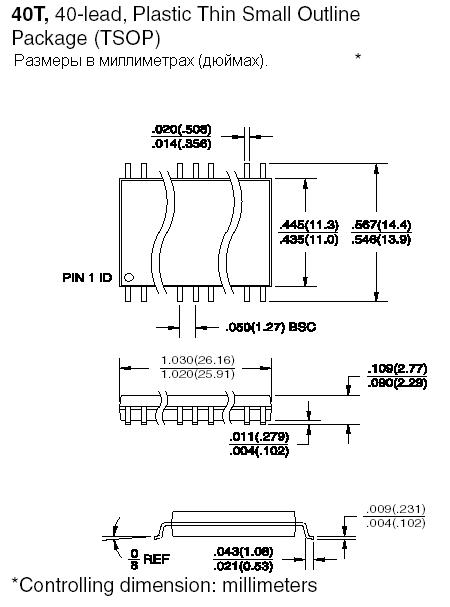

Информация для заказа.

| fSCK, МГц |

Icc, мА |

Код для заказа |

Корпус |

Исполнение |

| Рабочий |

В режиме ожидания |

| 20(1) |

10(1) |

0.01 |

AT45DB642-TC |

40T |

Коммерческое (0..70°С) |

| 20(1) |

10(1) |

0.01 |

AT45DB642-TI |

40T |

Промышленное

(-40..85°С) |

Прим: 1 Последовательный интерфейс.

40T – 40-выводный TSOP.

лимузины лимо авто - автосалон продажи роскошных автомоблилей в Москве

|