Раздел 20

Модуль АЦП SD16

Модуль АЦП SD16 представляет собой многоканальный 16-битный сигма-дельта аналогово-цифровой преобразователь. В это главе описана работа модуля АЦП SD16. Модуль SD16 присутствует в микроконтроллерах MSP430FE42x и MSP430F42x.

Содержание:

20.1 Модуль АЦП SD16 - введение

Модуль АЦП SD16 содержит до трёх независимых сигма-дельта аналогово-цифровых преобразователей и встроенный источник опорного напряжения. Каждый из АЦП имеет до восьми полностью дифференциальных переключаемых каналов, в том числе встроенный датчик температуры. АЦП созданы на базе дельта-сигма модуляторов второго порядка с передискретизацией и цифровых децимирующих фильтров. Для прореживания (децимации) используются фильтры comb-типа с программируемым коэффициентом прореживания до 256. Дополнительная фильтрация может быть осуществлена программно. Модуль АЦП SD16 обладает следующими свойствами:

- 16-битная сигма-дельта архитектура

- До 3-х независимо функционирующих каналов АЦП

- До 8 переключаемых дифференциальных аналоговых входов на канал

- Программно включаемый встроенный источник опорного напряжения (1,2В)

- Программный выбор встроенного или внешнего источника опорного напряжения

- Встроенный датчик температуры, доступный для всех каналов

- Входная частота модулятора до 1,048576 МГц (частота выборки fSAMPLE до 4096 Гц при передискретизации 256х)

- Программно выбираемый режим преобразования с пониженным энергопотреблением

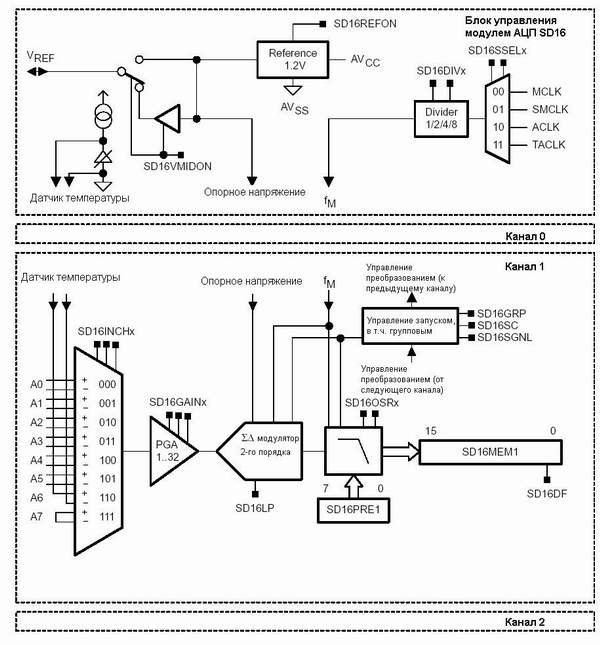

Блок схема модуля АЦП SD16 показана на рис. 20–1.

Рис. 20–1 Блок схема модуля АЦП SD16

20.2 Работа модуля АЦП SD16

Модуль АЦП SD16 конфигурируется при помощи пользовательского программного обеспечения. Настройка и функционирование модуля будут подробно рассмотрены ниже.

20.2.1 Ядро аналогово-цифрового преобразователя

Аналогово-цифровое преобразование осуществляется однобитным сигма-дельта модулятором второго порядка. Однобитный компаратор в составе модулятора осуществляет квантование сигнала с частотой модулятора fM. Получающийся в результате однобитовый поток усредняется цифровым фильтром, формируя результат преобразования.

20.2.2 Цифровой фильтр

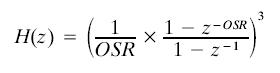

Цифровой фильтр обрабатывает 1-битный поток данных, поступающий с модулятора при помощи SINC3 фильтра comb-типа. Передаточная характеристика такого фильтра может быть представлена в Z-плоскости как:

а в частотной области как:

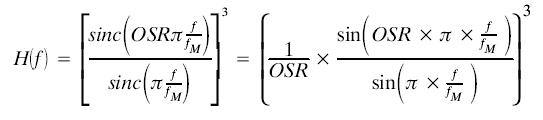

где степень передискретизации, OSR, это отношение частоты модулятора fM к частоте выборки fS. На рис. 20-2 показана частотная характеристика фильтра при OSR равном 32. Первый срез фильтра приходится на частоту fS = fM/OSR. Частота среза может быть подстроена изменением частоты модулятора, fM, при помощи бит SD16SSELx и SD16DIVx или степени передискретизации при помощи бит SD16OSRx. Цифровой фильтр для каждого из разрешённых каналов завершает прореживание (децимацию) цифрового потока данных и выдаёт результат преобразования в соответствующий регистр SD16MEMx с частотой выборки fS.

Рис. 20-2 Частотная характеристика фильтра при OSR равном 32

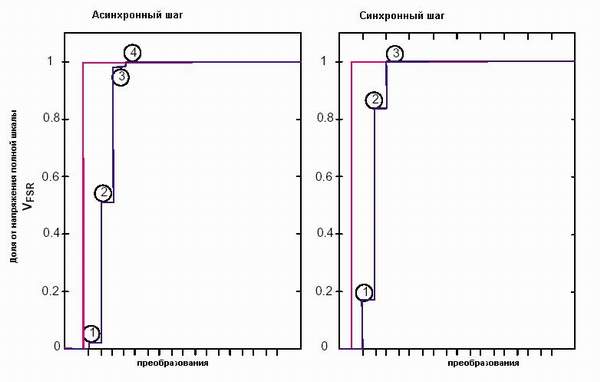

На рис. 20-3 показаны пошаговый отклик фильтра и точки преобразования. Для корректного пошагового преобразования после старта преобразования, следует выждать определенное время, называемое временем установления (settling time) до того момента, пока результат преобразования не станет корректным. Битами SD16INTDLYx можно задать время установления достаточное, для единовременного изменения сигнала на входе АЦП в пределах полной шкалы измерения. Если шаг преобразований синхронизирован с децимацией цифрового фильтра, корректный результат на выходе появится после третьего преобразования. Асинхронность этих сигналов потребует дополнительного цикла преобразования.

Рис. 20-3 Пошаговый отклик цифрового фильтра и точки преобразования

20.2.3 Диапазон аналогового сигнала и усилитель с программируемым коэффициентом усиления (PGA)

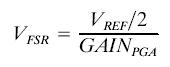

Полный диапазон входного аналогового сигнала для каждой пары входов зависит от установленного коэффициента усилителя по каждому каналу. Максимально допустимый диапазон — ±VFSR, где VFSR определяется как

При использовании опорного напряжения величиной 1.2В, максимальный диапазон входного сигнала при усилении 1 равен:

Конкретные значения допустимых значений входных сигналов см. в документации на конкретный тип МК.

20.2.4 Источник опорного напряжения

Модуль АЦП SD16 содержит встроенный источник опорного напряжения величиной 1.2В, который может быть использован для всех каналов модуля SD16 и включается битом SD16REFON. Для снижения помех при использовании встроенного источника опорного напряжения рекомендуется использование внешнего конденсатора ёмкостью в 100 нФ, подключенного между выводов VREF и AVSS. Опорное напряжение также может использоваться вне микроконтроллера, если это разрешено битом SD16VMIDON. Выход ИОН буферизован, нагрузочный ток буфера до 1мА. При использовании опорного напряжения вне микроконтроллера, требуется внешний конденсатор ёмкостью в 470 нФ, подключенный между выводов VREF и AVSS. Уточнённые параметры см. в документации на конкретный тип МК.

В том случае, если биты SD16REFON и SD16VMIDON обнулены, АЦП может использовать внешний ИОН, подключенный к выводу VREF.

20.2.5 Регистры памяти преобразований: SD16MEMx

Каждому каналу модуля SD16 сопоставлен регистр памяти SD16MEMx. На каждом шаге децимации цифрового фильтра результат преобразования записываются в соответствующий регистр SD16MEMx. При перезаписи нового значения в регистр SD16MEMx устанавливается бит SD16IFG. Бит SD16IFG обнуляется автоматически при чтении из регистра SD16MEMx либо может быть обнулён программно.

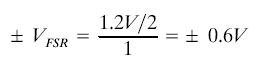

Формат выходных данных

Выходные данные могут иметь вид двоичного кода со смещением либо кода с дополнением до 2-х, как показано в Таблице 20-1.Формат данных определяется битом SD16DF.

| SD16DF |

Формат |

Напряжение на входе |

SD16MEMx* |

Выход цифрового фильтра (OSR = 256) |

| 0 |

Однополярный: двоичный код со смещением |

Максимум (+FSR) |

FFFF |

FFFFFF |

| Ноль |

8000 |

8000000 |

| Минимум (-FSR) |

0000 |

000000 |

| 1 |

Двухполярный: код с дополнением до 2-х |

Максимум (+FSR) |

7FFF |

7FFFFF |

| Ноль |

0000 |

800000 |

| Минимум (-FSR) |

8000 |

000000 |

* не зависит от настроек SD16OSRx; SD16LSBACC = 0.

На Рис. 20-4 показана связь между входным напряжением во всём диапазоне от минимума до максимума (-VFSR … +VFSR) и результатом преобразования. Проиллюстрирован результат для обоих типов формата данных.

Рис. 20-4 Зависимость результата преобразования от входного напряжения

Выход цифрового фильтра

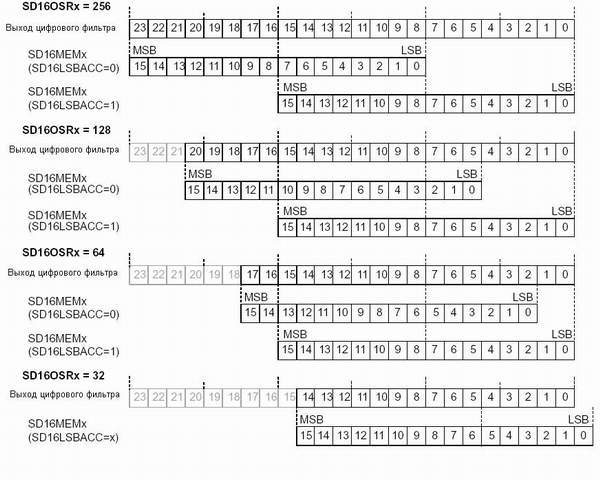

Число бит на выходе каждого из цифровых фильтров зависит от степени передискретизации и изменяется от 16 до 24. На Рис. 20-5 показан выход цифрового фильтра и его связь с содержимым регистров SD16MEMx для всех настроек бит SD16OSRx.

Биты SD16LSBACC и SD16LSBTOG позволяют иметь доступ к младшим значащим разрядам (МЗР) выхода цифрового фильтра. Когда SD16LSBACC = 1, 16 младших значащих разрядов выхода цифрового фильтра могут быть прочитаны через регистры SD16MEMx с помощью 16-битных инструкций. Доступ к регистрам SD16MEMx также может быть осуществлён при помощи байтовых инструкций (.B), возвращающих 8 МЗР выхода цифрового фильтра.

Когда SD16LSBTOG = 1, бит SD16LSBACC автоматически инвертируется каждый раз при чтении соответствующего каналу регистра SD16MEMx. Это позволяет прочитать результат преобразования на выходе цифрового фильтра полностью с помощью двух операций чтения регистра SD16MEMx. Установка или очистка бита SD16LSBTOG не влияет на состояние SD16LSBACC вплоть до следующего доступа к регистру SD16MEMx.

Диапазон положительных и отрицательных значений на выходе цифрового фильтра зависит от выбранного коэффициента передискретизации.

Рис. 20-5 Используемые биты на выходе цифрового фильтра

20.2.6 Выбор канала

Каждый канал модуля АЦП SD16 может осуществлять преобразование по восьми дифференциальным входам, мультиплексируемым на вход усилителя с программируемым коэффициентом усиления (PGA). До шести пар входов (A0-A5) имеют внешние выводы. По вопросу подключения аналоговых входов см. документацию на конкретный МК. Встроенный датчик температуры доступен в каждом канале АЦП по входу A6 мультиплексора. Вход A7 представляет собой перемычку между положительным и отрицательным входом пары и может быть использован для калибровки смещения в каждом входном каскаде модуля АЦП SD16.

Конфигурация аналогового входа

Конфигурация аналогового входа для всех каналов АЦП осуществляется при помощи регистров SD16INCTLx. Настройки, хранимые в этих регистрах независимы для каждого из каналов.

Битами SD16INCHx выбирается одна из восьми входных пар сигналов при помощи аналогового мультиплексора. Усиление для каждого PGA устанавливается битами SD16GAINx. Всего доступно 8 вариантов установки усиления.

Любые изменения бит SD16INCHx и SD16GAINx во время преобразования вступают в силу только на следующем шаге децимации цифрового фильтра. После изменения этих бит, последующие три результата преобразования могут быть некорректными из-за конечного времени установления цифрового фильтра. Эта проблема может быть разрешена аппаратно с помощью бит SD16INTDLYx. Если SD16INTDLY = 00h, запрос прерывания по завершению преобразования возникнет только после четвёртого по счёту преобразования после запуска.

20.2.7 Режимы преобразования

Модуль АЦП SD16 может работать в четырёх различных режимах .перечисленных в Таблице 20-2. Выбор режима преобразования для каждого канала устанавливается битами SD16SNGL и SD16GRP.

Таблица 20-2. Режимы преобразования

| SD16SNGL |

SD16GRP* |

Режим |

Описание |

| 1 |

0 |

Одиночное преобразование по одному каналу |

Значение по одному из каналов оцифровывается один раз |

| 0 |

0 |

Повторяющиеся преобразования по одному каналу |

Значение по одному из каналов оцифровывается постоянно |

| 1 |

1 |

Однократное групповое преобразование |

Значения по группе каналов оцифровываются один раз |

| 0 |

1 |

Повторяющиеся групповые преобразования |

Значения по группе каналов оцифровываются постоянно |

* Бит означает, что канал входит в группу и что канал является ведущим в группе в случае, если SD16GRP = 0 и если установлен бит SD16GRP предыдущего канала.

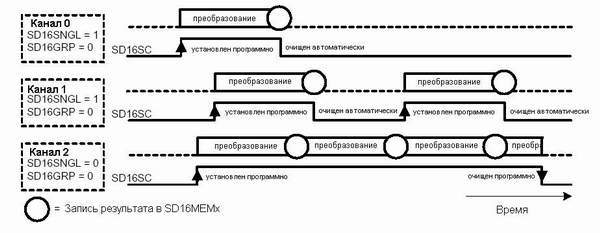

Одиночное преобразование по одному каналу

Установка в «1» бита SD16SC запускает одиночное преобразование для соответствующего канала в случае, если SD16SNGL = 1 и канал не сгруппирован с другими. Бит SD16SC очищается автоматически по завершению преобразования. Установка в «0» бита SD16SC в процессе преобразования немедленно прекращает процесс, питание канала и соответствующий цифровой фильтр отключаются. При этом значение в регистре SD16MEMx после очистки бита SD16SC может измениться. Ввиду этого, рекомендуется считывать результат преобразования из регистра SD16MEMx до очистки бита SD16SC в целях предотвращения считывания ложного результата.

Повторяющиеся преобразования по одному каналу

Выбор данного режима осуществляется установкой SD16SNGL = 0. Преобразование по выбранному каналу запускается установкой в «1» бита SD16SC продолжается до тех пор, пока SD16SC не будет программно очищен в том случае, канал не сгруппирован с другими.

Установка в «0» бита SD16SC в процессе преобразования немедленно прекращает процесс, питание канала и соответствующий цифровой фильтр отключаются. При этом значение в регистре SD16MEMx после очистки бита SD16SC может измениться. Ввиду этого, рекомендуется считывать результат преобразования из регистра SD16MEMx до очистки бита SD16SC в целях предотвращения считывания ложного результата.

На Рис. 20-6 показан процесс преобразования по одиночному каналу в режимах одиночного и повторяющихся преобразований.

Рис. 20-6 Процесс преобразования по одиночному каналу

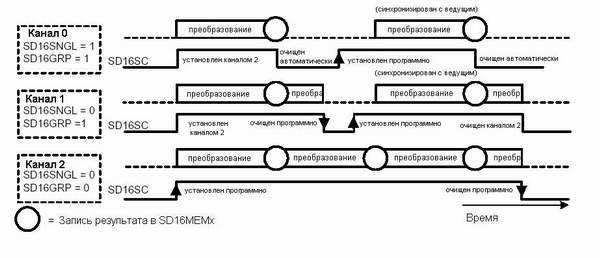

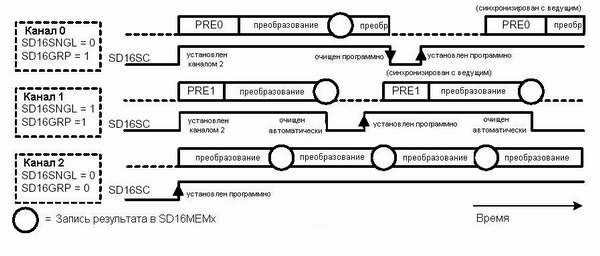

Однократное групповое преобразование

Последовательные каналы модуля АЦП SD16 могут быть сгруппированы с помощью бита SD16GRP для синхронизации преобразований. Установка бита SD16GRP для определённого канала группирует данный канал с последующим в модуле. Например, установка бита SD16GRP для 0-го канала группирует его с 1-ым каналом. В этом случае 1-ый канал является ведущим, его битом SD16SC разрешаются и запрещаются преобразования для всех остальных каналов группы. Бит SD16GRP ведущего канала всегда равен нулю. Бит SD16GRP последнего канала модуля АЦП SD16 является незначащим и также всегда равен нулю.

Если для канала в составе группы установлено SD16SNGL = 1, для этого канала будет выбран режим однократного преобразования. Одиночное преобразование по этому каналу будет осуществляться синхронно с установкой в «1» бита SD16SC ведущего канала. Бит SD16SC для всех каналов в группе автоматически управляется битом SD16SC ведущего канала. Программная очистка бита SD16SC может осуществляться для каждого канала независимо.

Установка в «0» бита SD16SC ведущего канала в процессе преобразования немедленно прекращает процесс преобразования по всем каналам в группе, питание каналов и соответствующие цифровые фильтры отключаются. При этом значения в регистрах SD16MEMx после очистки бита SD16SC может измениться. Ввиду этого, рекомендуется считывать результат преобразования из регистров SD16MEMx до очистки бита SD16SC в целях предотвращения считывания ложного результата.

Повторяющиеся групповые преобразования

Когда SD16SNGL = 0 для канала в составе группы, для данного канала выбран режим повторяющихся преобразований. Повторяющееся преобразование по этому каналу будет осуществляться синхронно с установкой в «1» бита SD16SC ведущего канала. Бит SD16SC для всех каналов в группе автоматически управляется битом SD16SC ведущего канала. Программная очистка бита SD16SC может осуществляться для каждого канала независимо.

Когда бит SD16SC для канала в составе группы программно установлен в «1» независимо от ведущего канала, преобразование по данному каналу будет автоматически синхронизировано с преобразованием по ведущему каналу. Таким образом, обеспечивается гарантированная синхронность преобразования сгруппированных каналов с преобразованием по ведущему каналу.

Установка в «0» бита SD16SC ведущего канала в процессе преобразования немедленно прекращает процесс преобразования по всем каналам в группе, питание каналов и соответствующие цифровые фильтры отключаются. При этом значения в регистрах SD16MEMx после очистки бита SD16SC может измениться. Ввиду этого, рекомендуется считывать результат преобразования из регистров SD16MEMx до очистки бита SD16SC в целях предотвращения считывания ложного результата.

На Рис. 20-7 показан процесс преобразования для трёх сгруппированных каналов модуля АЦП SD16. Два канала настроены на режим однократного преобразования, SD16SNGL = 1, а ведущий канал функционирует в повторяющемся режиме, SD16SNGL = 0.

Обратите внимание, что преобразования по всем каналам осуществляются синхронно с ведущим каналом вне зависимости от программной установки индивидуальных бит SD16SC для ведомых каналов.

Рис. 20-7 Процесс преобразования для трёх сгруппированных каналов

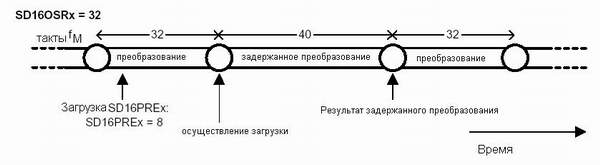

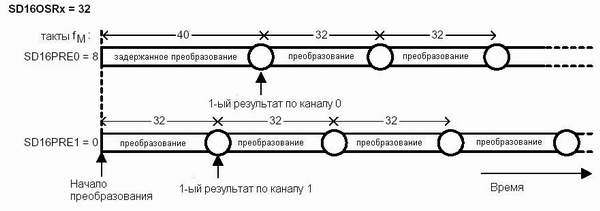

20.2.8 Режим преобразования с предварительной загрузкой

Когда несколько каналов сгруппированы, регистры SD16PREx могут быть использованы за задания задержки преобразования для каждого канала. При использовании SD16PREx, время децимации цифрового фильтра возрастает на определённое число тактов частоты fM , находящееся в диапазоне от 0 до 255. На рис. 20-8 показан пример использования регистров SD16PREx.

Рис. 20-8 Преобразование с предварительной загрузкой

Задержка преобразования, записанная в SD16PREx, вступает в силу с начала следующего цикла преобразования после того, в котором она была записана. Задержка имеет действие только во время первого преобразования после установки бита SD16SC, следующего за записью в регистр SD16PREx. Последующие преобразования осуществляются в обычном режиме. После изменения содержимого регистров SD16PREx, следующая запись в эти регистры должна производиться не ранее, чем по завершению следующего цикла преобразования, в противном случае результаты преобразования могут быть некорректными.

Точность результата задержанного преобразования зависит от длины задержки, записанной в SD16PREx и от частоты оцифровываемого аналогового сигнала. Например, при измерении постоянного сигнала, задержка SD16PREx не влияет на результат преобразования вне зависимости от её длительности. Целесообразность использования режима задержанного преобразования определяется пользователем.

На рис. 20-9 показана работа сгруппированных каналов 0 и 1. Регистр предварительной загрузки канала 1 обнулён, что соответствует немедленному запуску преобразования, преобразование по каналу 0 задержано установкой SD16PRE0 = 8. Первое преобразование по каналу 0 с задержкой SD16PREx = 8 приводит к сдвигу всех последующих преобразований на время, равное 8 тактов частоты fM.

Рис. 20-9 Запуск преобразования с предварительной загрузкой

Следует соблюдать осторожность в том случае, если один канал или группа каналов функционируют в режиме однократного преобразования или программно запрещены в то время, как ведущий канал остаётся активным. Каждый раз после того, как канал в группе будет разрешён по новой и засинхронизирован с ведущим, значение задержки для этого канала будет использовано снова. На рис. 20-10 показан процесс синхронизации и применения задержек к каналам в группе. Рекомендуется задавать для ведущего канала SD16PREx = 0 для сохранения значений задержек между ведущим и ведомыми каналами при запрещении и последующем разрешении последних.

Рис. 20-10 Предварительная загрузка и синхронизация каналов

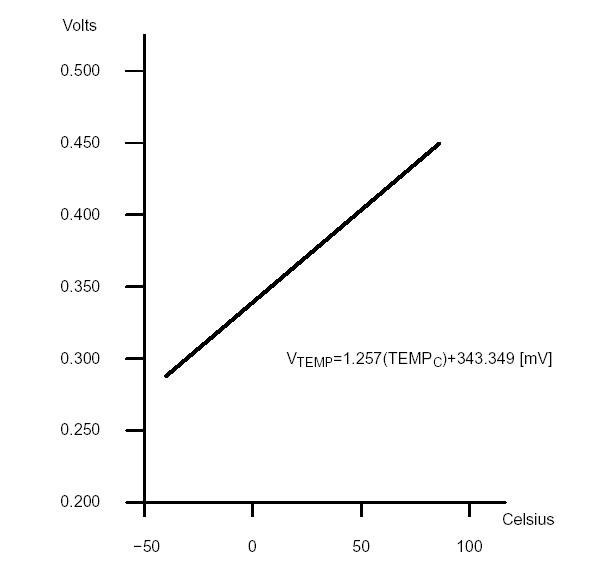

20.2.9 Использование встроенного датчика температуры

Для использования встроенного датчика температуры пользователь должен выбрать входной аналоговый канал SD16INCHx = 110. Все остальные настройки, включая настройки регистров SD16INTDLYx и SD16GAINx, конфигурируются аналогично, как и для случая использования внешних входов.

Типовая характеристика температурной зависимости датчика приведена на рис. 20-11.

После переключения входа АЦП SD16 на температурный датчик следует выждать определённое время, используя для этого регистр SD16INTDLYx, для установления цифрового фильтра. В противном случае результаты могут быть некорректными. Характеристика температурного датчика может иметь значительное смещение, поэтому для многих применений может потребоваться калибровка. Уточнённые параметры датчика температуры см. в документации на конкретный тип МК.

Рис. 20-11 Типовая характеристика датчика температуры

20.2.10 Обработка прерываний

Модуль АЦП имеет 2 источника прерываний для каждого из каналов:

Биты SD16IFG устанавливаются, когда в соответствующий регистр памяти SD16MEMx записывается результат преобразования. В случае, если установлен соответствующий бит SD16IE и бит GIE в такой ситуации генерируется запрос прерывания. Флаг переполнения SD16OVIFG устанавливается, если результат преобразования записывается в регистр памяти SD16MEMx ранее, чем был прочитан результат предыдущего преобразования.

Генерация векторов прерывания модуля АЦП SD16IV

Все источники прерываний модуля АЦП SD16 имеют собственный приоритет, но скомбинированы в один вектор прерываний. Регистр SD16IV используется для определения конкретного источника, вызвавшего прерывание модуля SD16. Разрешённый источник прерывания с максимальным приоритетом формирует число в регистре SD16IV (см. описание регистра). Это число может программно обработано либо просто добавлено к программному счётчику для автоматического перехода на соответствующую подпрограмму обработки. Запрет прерываний от модуля SD16 не влияет на значение в регистре SD16IV.

Любой доступ к регистру SD16IV, будь то чтение либо запись, не влияет на флаги SD16OVIFG и SD16IFG. Флаги SD16IFG сбрасываются при чтении соответствующего регистра памяти SD16MEMx либо могут быть очищены программно. Флаги SD16OVIFG могут быть очищены только программно.

Если во время обработки прерывания возникает следующее прерывание, для него также будет сгенерирован запрос прерывания. Например, если возникает прерывание по флагу SD16OVIFG и одному (либо более) флагу SD16IFG в то время как обработчик прерывания обращается к регистру SD16IV, прерывание по флагу SD16OVIFG будет обработано первым, а соответствующий флаг (либо флаги) должен быть программно очищен. После выполнения инструкции RETI обработчика, флаг SD16IFG с наибольшим прерыванием вызовет следующий запрос прерывания.

Задержка прерываний

Биты SD16INTDLYx управляют временными задержками генерации запроса прерываний для соответствующего канала. Эта опция позволяет задержать запрос прерывания после завершения преобразования на время до четырёх циклов преобразования для формирования времени установления цифрового фильтра. Эта задержка применяется каждый раз после установки бита SD16SC либо после изменения бит SD16GAINx или SD16INCHx для соответствующего канала. Кроме этого, SD16INTDLYx задерживает генерацию прерывания по переполнению для данного канала на выбранное значение циклов задержки. Запросы прерывания в течение этих циклов для задержанных преобразований не генерируются.

Пример программы обработчика прерываний модуля АЦП SD16

Приведенный ниже пример программы рекомендуется для обслуживания регистра SD16IV ввиду наименьших программных затрат на обработку. Содержимое регистра SD16IV добавляется к программному счётчику PC, автоматически генерируя переход на соответствующий обработчик.

Число в правом поле показывает количество тактов ЦПУ для каждой инструкции. Показанные программные затраты включают вызов прерывания и возврат из него и не включают собственно обслуживание задачи. Общие программные затраты в тактах:

- SD16OVIFG, CH0 SD16IFG, CH1 SD16IFG 16 тактов

- CH2 SD16IFG 14 тактов

Обработка прерывания канала 2 SD16IFG даёт пример непосредственной проверки источника с наибольшим приоритетом в обработчике прерывания. Такой подход позволяет сэкономить 9 тактов в том случае, если потребуется обработка ещё одного прерывания модуля SD16.

; Обработчик прерываний модуля АЦП SD16.

INT_SD16 ; Вход в обработчик 6

ADD &SD16IV,PC ; Прибавить смещение к PC 3

RETI ; Вектор 0: нет источника 5

JMP ADOV ; Вектор 2: переполнение АЦП 2

JMP ADM0 ; Вектор 4: CH_0 SD16IFG 2

JMP ADM1 ; Вектор 6: CH_1 SD16IFG 2

;

; Обработка CH_2 SD16IFG. Оператор JMP не нужен.

;

ADM2 MOV &SD16MEM2,xxx ; Чтение результата, очистка флага

... ; Остальные инструкции, если требуется

JMP INT_SD16 ; Проверка следующего запроса прерывания

;

; Обработка остальных источников

;

ADM1 MOV &SD16MEM1,xxx ; Чтение результата, очистка флага

... ; Остальные инструкции, если требуется

RETI ; Возврат из прерывания 5

;

ADM0 MOV &SD16MEM0,xxx ; Чтение результата, очистка флага

RETI ; Возврат из прерывания 5

;

ADOV ... ; Обработка переполнения SD16MEMx

RETI ; Возврат из прерывания 5

20.3 Регистры модуля АЦП SD16

Регистры модуля контроллера ЖКИ перечислены в таблице 20–3.

Таблица 20–3

| Регистр |

Краткое название |

Тип |

Адрес |

Начальное состояние |

| Регистр управления модулем АЦП SD16 |

SD16CTL |

Чтение/запись |

0100h |

Обнулён по сбросу PUC |

| Вектор прерываний модуля АЦП SD16 |

SD16IV |

Чтение/запись |

0110h |

Обнулён по сбросу PUC |

| Регистр управления канала 0 модуля АЦП SD16 |

SD16CCTL0 |

Чтение/запись |

0102h |

Обнулён по сбросу PUC |

| Регистр памяти преобразования канала 0 модуля АЦП SD16 |

SD16MEM0 |

Чтение/запись |

0112h |

Обнулён по сбросу PUC |

| Регистр управления входами канала 0 модуля АЦП SD16 |

SD16INCTL0 |

Чтение/запись |

0B0h |

Обнулён по сбросу PUC |

| Регистр предварительной загрузки канала 0 модуля АЦП SD16 |

SD16PRE0 |

Чтение/запись |

0B8h |

Обнулён по сбросу PUC |

| Регистр управления канала 1 модуля АЦП SD16 |

SD16CCTL1 |

Чтение/запись |

0104h |

Обнулён по сбросу PUC |

| Регистр памяти преобразования канала 1 модуля АЦП SD16 |

SD16MEM1 |

Чтение/запись |

0114h |

Обнулён по сбросу PUC |

| Регистр управления входами канала 1 модуля АЦП SD16 |

SD16INCTL1 |

Чтение/запись |

0B1h |

Обнулён по сбросу PUC |

| Регистр предварительной загрузки канала 1 модуля АЦП SD16 |

SD16PRE1 |

Чтение/запись |

0B9h |

Обнулён по сбросу PUC |

| Регистр управления канала 2 модуля АЦП SD16 |

SD16CCTL2 |

Чтение/запись |

0106h |

Обнулён по сбросу PUC |

| Регистр памяти преобразования канала 2 модуля АЦП SD16 |

SD16MEM2 |

Чтение/запись |

0116h |

Обнулён по сбросу PUC |

| Регистр управления входами канала 2 модуля АЦП SD16 |

SD16INCTL2 |

Чтение/запись |

09Eh |

Обнулён по сбросу PUC |

| Регистр предварительной загрузки канала 2 модуля АЦП SD16 |

SD16PRE2 |

Чтение/запись |

0BAh |

Обнулён по сбросу PUC |

SD16CTL, Регистр управления модулем АЦП SD16

| r0 |

r0 |

r0 |

r0 |

r0 |

r0 |

r0 |

rw-0 |

| SD16DIVx |

SD16SSELx |

SD16VMIDON |

SD16REFON |

SD16OVIE |

Резервный |

| rw-0 |

rw-0 |

rw-0 |

rw-0 |

rw-0 |

rw-0 |

rw-0 |

r0 |

| Резервные |

Биты 15-9 |

Резервные |

| SD16LP |

Бит 8 |

Режим пониженного потребления. Этим битом выбирается режим работы АЦП SD16 с пониженной скоростью и пониженным энергопотреблением.

0 - режим пониженного потребления выключен

1 - режим пониженного потребления включен, максимальная тактовая частота модуля SD16 снижена. |

| SD16DIVx |

Биты 7-6 |

Делитель тактовой частоты модуля SD16

00 /1

01 /2

10 /4

11 /8 |

| SD16SSELx |

Биты 5-4 |

Выбор источника тактирования модуля SD16

00 MCLK

01 SMCLK

10 ACLK

11 Внешняя TACLK |

| SD16VMIDON |

Бит 3 |

Включение буфера VMID

0 выключен

1 включен |

| SD16REFON |

Бит 2 |

Включение источника опорного напряжения

0 выключен

1 включен |

| SD16OVIE |

Бит 1 |

Разрешение прерывания по переполнению модуля SD16. Для разрешения также следует установить бит GIE.

0 Прерывание по переполнению запрещено

1 Прерывание по переполнению разрешено |

| Резервный |

Бит 0 |

Резервный |

SD16СCTLx, Регистр управления канала x модуля АЦП SD16

| Резервные |

SD16SNGL |

SD16OSRx |

| последний адрес чтения автомата PSM |

| r0 |

r0 |

r0 |

r0 |

r0 |

r0 |

r0 |

rw-0 |

SD16

LSBTOG |

SD16

LSBACC |

SD16

OVIFG |

SD16DF |

SD16IE |

SD16IFG |

SD16SC |

SD16GRP |

| rw-0 |

rw-0 |

rw-0 |

rw-0 |

rw-0 |

rw-0 |

rw-0 |

r0 |

| Резервные |

Биты 15-11 |

Резервные |

| SD16SNGL |

Бит 10 |

Выбор режима одиночного преобразования

0 режим повторяющихся преобразований

1 режим одиночного преобразования |

| SD16OSRx |

Биты 9-8 |

Степень передискредизации

00 256

01 128

10 64

11 32 |

| SD16LSBTOG |

Бит 7 |

Инверсия МЗР. Когда этот бит установлен, SD16LSBACC инвертируется каждый раз при чтении регистра SD16MEMx.

0 SD16LSBACC не инвертируется при чтении регистра SD16MEMx

1 SD16LSBACC инвертируется при чтении регистра SD16MEMx |

| SD16LSBACC |

Бит 6 |

Доступ к МЗР. Этот бит определяет доступ к старшим либо младшим 16 битам результата преобразования модуля SD16.

0 SD16MEMx содержит СЗР преобразования.

1 SD16MEMx содержит МЗР преобразования. |

| SD16OVIFG |

Бит 5 |

Флаг прерывания по переполнению модуля SD16

0 нет прерывания по переполнению

1 есть прерывание по переполнению |

| SD16DF |

Бит 4 |

Формат кода данных модуля SD16

0 двоичный со смещением

1 дополнительный до двух |

| SD16IE |

Бит 3 |

Разрешение прерываний модуля SD16

0 запрещены

1 разрешены |

| SD16IFG |

Бит 2 |

Флаг прерывания модуля SD16. SD16IFG выставляется, когда готовы результаты преобразования. Флаг SD16IFG сбрасывается автоматически при чтении из соответствующего регистра SD16MEMx либо может быть очищен программно.

0 прерывания нет

1 прерывание есть |

| SD16SC |

Бит 1 |

Запуск преобразования модуля SD16

0 нет запуска преобразования

1 есть запуск преобразования |

| SD16GRP |

Бит 0 |

Группировка каналов модуля SD16. Группирует канал с последующим. В последнем канале не используется.

0 не сгруппирован

1 сгруппирован |

SD16INCTLx, Регистр управления входами канала x модуля АЦП SD16

| SD16INTDLYx |

SD16GAINx |

SD16INCHx |

| rw-0 |

rw-0 |

rw-0 |

rw-0 |

rw-0 |

rw-0 |

rw-0 |

rw-0 |

| SD16INTDLYx |

Биты 7-6 |

Задержка генерации прерывания после запуска преобразования. Этими битами выбирается величина задержки в циклах преобразования.

00 прерывание вызывается после четвёртого преобразования

01 прерывание вызывается после третьего преобразования

10 прерывание вызывается после второго преобразования

11 прерывание вызывается после первого преобразования |

| SD16GAINx |

Биты 5-3 |

Выбор коэффициента усиления предварительного усилителя модуля SD16

000 x1

001 x2

010 x4

011 x8

100 x16

101 x32

110 зарезервировано

111 зарезервировано |

| SD16INCHx |

Биты 2-0 |

Выбор входной дифференциальной пары модуля SD16

000 A0

001 A1

010 A2

011 A3

100 A4

101 A5

110 A6- датчик температуры

111 A7- перемычка для калибровки PGA |

SD16MEMx, Регистр памяти преобразования канала x модуля АЦП SD16

| Результат преобразования |

Биты 15-0 |

Результат преобразования. В регистре SD16MEMx хранятся данные старших или младших 16 бит с выхода цифрового фильтра в зависимости от состояния бита SD16LSBACC. |

SD16PREx, Регистр предварительной загрузки канала x модуля АЦП SD16

| Значение загрузки |

Биты 7-0 |

Значение предварительной загрузки для цифрового фильтра |

SD16IV, Регистр векторов прерываний модуля АЦП SD16

| r0 |

r0 |

r0 |

r-0 |

r-0 |

r-0 |

r-0 |

r0 |

| Биты 15-0 |

Вектор прерываний модуля SD16 |

| Содержимое SD16IV |

Источник прерывания |

Флаг прерывания |

Приоритет |

| 000h |

Нет прерываний |

- |

|

| 002h |

Переполнение SD16MEMx |

SD16CCTLx

SD16OVIFG* |

Наивысший |

| 004h |

Прерывание от SD16_0 |

SD16CCTL0

SD16IFG |

|

| 006h |

Прерывание от SD16_1 |

SD16CCTL1

SD16IFG |

|

| 008h |

Прерывание от SD16_2 |

SD16CCTL2

SD16IFG |

|

| 00Ah |

Зарезервировано |

— |

|

| 00Ch |

Зарезервировано |

— |

|

| 00Eh |

Зарезервировано |

— |

|

| 010h |

Зарезервировано |

— |

Низший |

|

* При возникновении переполнения SD16, пользователь должен проверить все флаги SD16CCTLx и SD16OVIFG для определения источника переполнения.

|