Раздел 18

Контроллер ЖКИ

Модуль контроллера ЖКИ поддерживает статические ЖКИ и ЖКИ с коэффициентом мультиплексирования 2,3 и 4 (2-mux, 3-mux, 4-mux). Модуль контроллера ЖКИ присутствует во всех микроконтроллерах семейства MSP430x4xx.

Содержание:

18.1 Модуль контроллера ЖКИ - введение

Модуль контроллера ЖКИ непосредственно управляет жидкокристаллическими индикаторами, автоматически генерируя требуемые для них переменные напряжения на выводах строк и сегментов. Модуль контроллера ЖКИ, встроенный в микроконтроллеры MSP430, поддерживает статические ЖКИ и ЖКИ с коэффициентом мультиплексирования 2,3 и 4 (2-mux, 3-mux, 4-mux).Модуль контроллера ЖКИ обладает следующими свойствами:

- Дисплейная память

- Автоматическая генерация сигналов управления

- Программно устанавливаемая частота обновления индикации

- Возможность мигания

- Поддержка четырёх типов ЖКИ:

- Статических

- С коэффициентом мультиплексирования 2 и смещением 1/2 ( 2-mux, 1/2 bias)

- С коэффициентом мультиплексирования 3 и смещением 1/3 ( 2-mux, 1/3 bias)

- С коэффициентом мультиплексирования 4 и смещением 1/3 ( 2-mux, 1/3 bias)

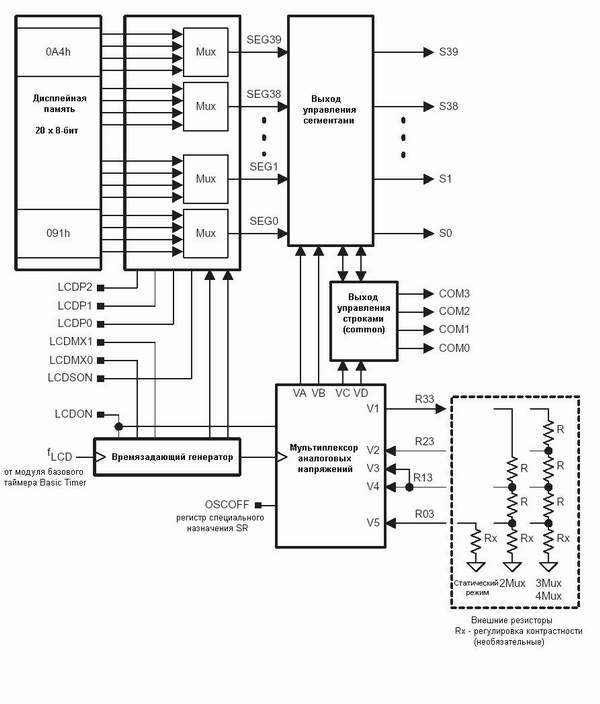

Блок схема модуля контроллера ЖКИ показана на рис. 18–1.

|

Примечание: максимальное количество сегментов ЖКИ

Различных микроконтроллеры семейства имеют разное максимально допустимое число сегментов ЖКИ:

- Микроконтроллеры ‘41x: от S0 до S23

- Микроконтроллеры ‘42x: от S0 до S31

- Микроконтроллеры ‘43x: от S0 до S31 (в 80-выводном корпусе) или от S0 до S39 (в 100-выводном корпусе)

- Микроконтроллеры ‘44x: от S0 до S39

|

Рис. 18–1 Блок схема модуля контроллера ЖКИ

18.2 Работа модуля контроллера ЖКИ

Модуль контроллера ЖКИ конфигурируется при помощи пользовательского программного обеспечения. Настройка и функционирование модуля будут подробно рассмотрены ниже.

18.2.1 Дисплейная память

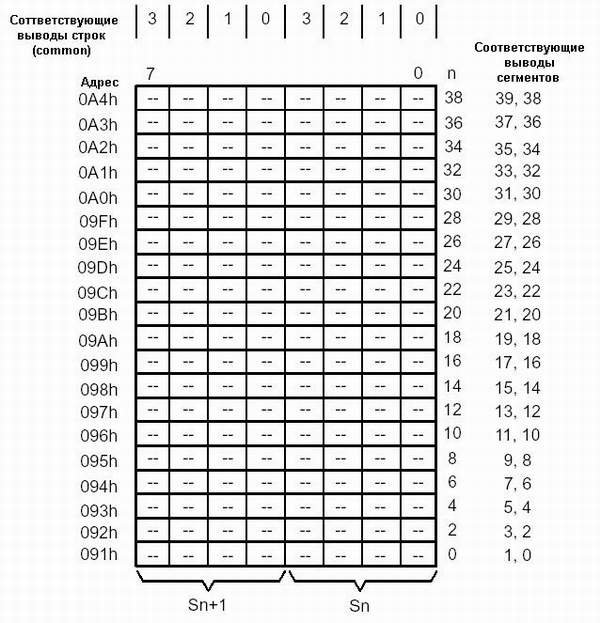

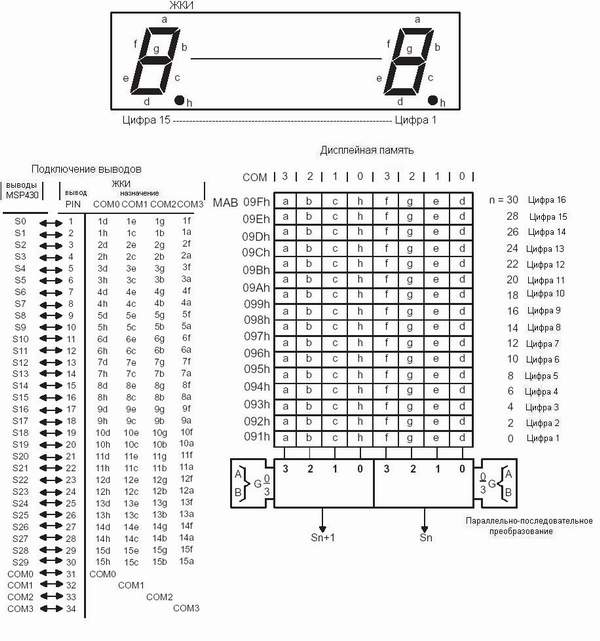

Карта памяти модуля контроллера ЖКИ показана на рис. 18-2. Каждый бит дисплейной памяти либо соответствует одному сегменту ЖКИ, либо не используется, в зависимости от установленного режима работы. Для включения сегмента ЖКИ следует установить в «1» соответствующий бит.

Рис. 18-2 Дисплейная память модуля контроллера ЖКИ

18.2.2 Мигание ЖКИ

Модуль контроллера ЖКИ поддерживает мигание. Над каждым битом в дисплейной памяти производится операция «логическое И» с битом LCDSON. Когда LCDSON =1, каждый сегмент либо включен, либо выключен, в зависимости от значения соответствующего бита в дисплейной памяти. Когда LCDSON =0, все сегменты выключены.

18.2.3 Генерация тактовых сигналов

Для генерации тактовых сигналов, управляющих строками и сегментами, модуль контроллера ЖКИ использует сигнал fLCD от модуля базового таймера Basic Timer1. Необходимая частота сигнала fLCD зависит от требований по частоте обновления индикации ЖКИ и от степени мультиплексирования. См. главу Базовый таймер Basic Timer1 по части дополнительной информации о конфигурировании частоты fLCD.

18.2.4 Генерация напряжений ЖКИ

Требуемые для ЖКИ уровни напряжений формируются извне и подаются на выводы R33, R23, R13 и R03. Аналоговые напряжения на этих выводах формируются резистивными делителями с соответствующими весовыми коэффициентами, как показано в Таблице 18-1. Типовое значение для R – 680кОм. В зависимости от типа ЖКИ могут применяться резисторы от 100кОм до 1МОм. Вывод R33 представляет собой коммутируемый выход питания VCC. Это даёт возможность отключать резистивный делитель, снижая энергопотребление в те моменты, когда ЖКИ не используется.

Таблица 18-1. Внешние аналоговые напряжения для модуля контроллера ЖКИ.

| OSCOFF |

LCDMXx |

LCDON |

VA |

VB |

VC |

VD |

R33 |

| x |

xx |

0 |

0 |

0 |

0 |

0 |

Выключен |

| 1 |

xx |

x |

0 |

0 |

0 |

0 |

Выключен |

| 0 |

00 |

1 |

V5/V1 |

V1/V5 |

V5/V1 |

V1/V5 |

Включен |

| 0 |

01 |

1 |

V5/V1 |

V1/V5 |

V3/V3 |

V1/V5 |

Включен |

| 0 |

1x |

1 |

V5/V1 |

V2/V4 |

V4/V2 |

V1/V5 |

Включен |

Контроль контрастности ЖКИ

Контроль контрастности ЖКИ может осуществляться извне регулировкой напряжения на выводе R03. Как правило, такая регулировка осуществляется подключением дополнительного резистора RX на землю. Увеличение напряжения на выводе R03 уменьшает эквивалентное напряжение на сегментах, что, в свою очередь, приводит к снижению контрастности.

18.2.5 Выходы модуля контроллера ЖКИ

Некоторые из выходов сегментов, строк и RXX модуля контроллера ЖКИ мультиплексированы со входами/выходами общего назначения процессора. Такие выводы могут быть использованы как в качестве цифровых входов/выходов, так и в качестве выходов модуля контроллера ЖКИ. Функция выводов СОМх и Rxx, если они мультиплексированы с цифровыми входами/выходами, определяются состоянием бит PxSELx, как описано в главе Цифровые входы/выходы. Функция выводов сегментов ЖКИ, если они мультиплексированы с цифровыми входами/выходами, определяются состоянием бит LCDPx. Биты LCDPx определяют состояние выводов по группам. Когда LCDPx =0, ни один из выводов не является выходом модуля контроллера ЖКИ. Когда LCDPx =1, в качестве выходов модуля контроллера ЖКИ функционируют выводы S0-S15. Когда LCDPx >1, выводы сегментов подключаются к Модулу контроллера ЖКИ группами по четыре. Например, если LCDPx =2, в качестве выходов модуля контроллера ЖКИ функционируют выводы S0-S19.

|

Примечание: Биты LCDPx не влияют на обособленные сегментные выводы контроллера ЖКИ,

Биты LCDPx влияют только на те выводы, которые имеют функции, переключаемые между выходами контроллера ЖКИ и цифровыми входами/выходами. На обособленные сегментные выходы контроллера ЖКИ биты LCDPx влияния не оказывают.

|

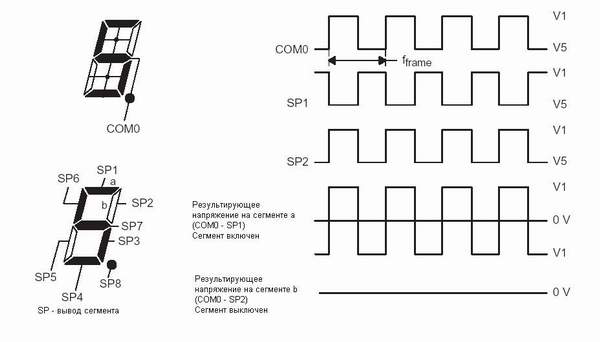

18.2.6 Статический режим

В статическом режиме каждый из сегментных выходов микроконтроллера MSP430 управляет одним сегментом ЖКИ, при этом используется только одна строка, COM0. На рис. 18–4 показаны примеры осциллограмм сигналов в статическом режиме.

Рис. 18–4 Примеры осциллограмм сигналов в статическом режиме

На рис. 18-5 показан пример статического ЖКИ, его подключение к MSP430 и карта сегментов. Обратите внимание, что это всего лишь пример, реальная карта сегментов в каждом конкретном случае будет зависеть от расположения выводов ЖКИ и его подключения к MSP430.

Рис. 18-5 Пример статического ЖКИ

Пример программы для статического режима

; Все восемь сегментов цифры как правило расположены

; в четырёх байтах дисплейной памяти при использовании статического режима.

;

a EQU 001h

b EQU 010h

c EQU 002h

d EQU 020h

e EQU 004h

f EQU 040h

g EQU 008h

h EQU 080h

; Будет отображаться содержимое регистра Rx.

: Таблица представляет включенные сегменты в соответствии

; с содержимым Rx

MOV.B Table (Rx),RY ; Загрузить расположение сегментов

; в служебную область памяти.

; (Ry) = 0000 0000 hfdb geca

MOV.B Ry,&LCDn ; Примечание:

; Записываются все биты

; байта памяти ЖКИ

RRA Ry ; (Ry) = 0000 0000 0hfd bgec

MOV.B Ry,&LCDn+1 ; Примечание:

; Записываются все биты

; байта памяти ЖКИ

RRA Ry ; (Ry) = 0000 0000 00hf dbge

MOV.B Ry,&LCDn+2 ; Примечание:

; Записываются все биты

; байта памяти ЖКИ

RRA Ry ; (Ry) = 0000 0000 000h fdbg

MOV.B Ry,&LCDn+3 ; Примечание:

; Записываются все биты

; байта памяти ЖКИ

...........

...........

;

Table DB a+b+c+d+e+f ; отображает ”0”

DB b+c ; отображает ”1”

...........

...........

DB

...........

18.2.7 Режим двойного мультиплексирования (2-Mux)

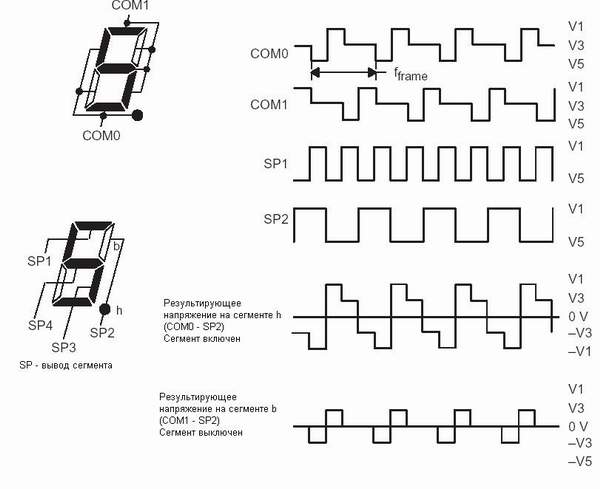

В режиме двойного мультиплексирования каждый сегментный выход микроконтроллера MSP430 управляет двумя сегментами ЖКИ, при этом используется две линии строк, COM0 и COM1. На Рис. 18–6 показаны примеры осциллограмм сигналов в режиме двойного мультиплексирования.

Рис. 18–6 Примеры осциллограмм сигналов в режиме двойного мультиплексирования

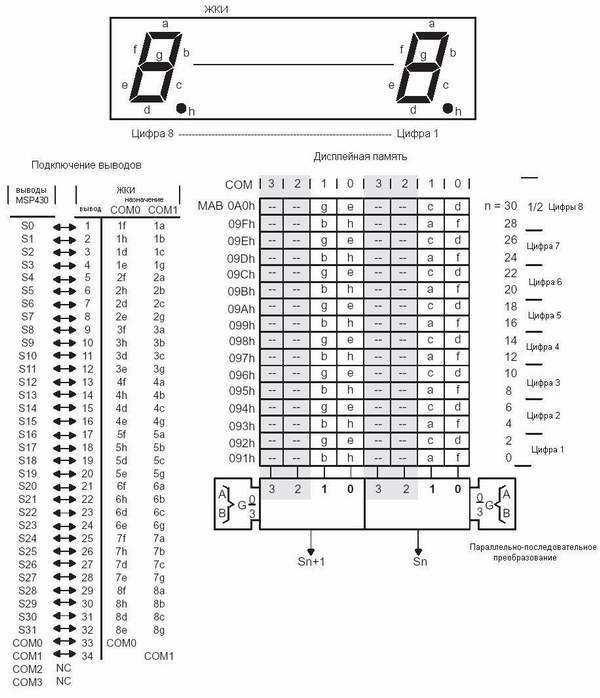

На рис. 18-7 показан пример ЖКИ в режиме двойного мультиплексирования, его подключение к MSP430 и карта сегментов. Обратите внимание, что это всего лишь пример, реальная карта сегментов в каждом конкретном случае будет зависеть от расположения выводов ЖКИ и его подключения к MSP430.

Рис. 18-7 Пример ЖКИ в режиме двойного мультиплексирования

Пример программы для режима двойного мультиплексирования

; Все восемь сегментов цифры как правило расположены

; в двух байтах дисплейной памяти при использовании

; режима двойного мультиплексирования.

a EQU 002h

b EQU 020h

c EQU 008h

d EQU 004h

e EQU 040h

f EQU 001h

g EQU 080h

h EQU 010h

; Будет отображаться содержимое регистра Rx.

: Таблица представляет включенные сегменты в соответствии

; с содержимым Rx

MOV.B Table (Rx),RY ; Загрузить расположение сегментов

; в служебную область памяти.

; (Ry) = 0000 0000 gebh cdaf

MOV.B Ry,&LCDn ; Примечание:

; Записываются все биты

; байта памяти ЖКИ

RRA Ry ; (Ry) = 0000 0000 0geb hcda

RRA Ry ; (Ry) = 0000 0000 00ge bhcd

MOV.B Ry,&LCDn+1 ; Примечание:

; Записываются все биты

; байта памяти ЖКИ

...........

...........

...........

Table DB a+b+c+d+e+f ; отображает ”0”

...........

DB a+b+c+d+e+f+g+ ; отображает ”8”

...........

...........

DB

...........

18.2.8 Режим тройного мультиплексирования (3-Mux)

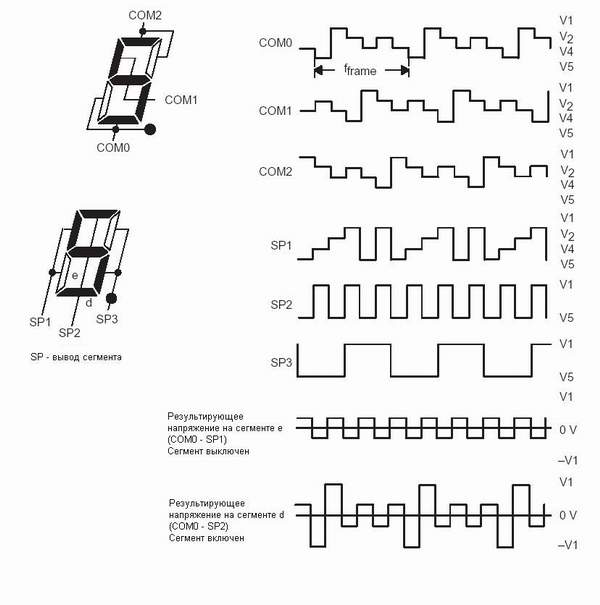

В режиме двойного мультиплексирования каждый сегментный выход микроконтроллера MSP430 управляет тремя сегментами ЖКИ, при этом используется три линии строк, COM0, COM1 и COM2. На Рис. 18–8 показаны примеры осциллограмм сигналов в режиме двойного мультиплексирования.

Рис. 18–8 Примеры осциллограмм сигналов в режиме тройного мультиплексирования

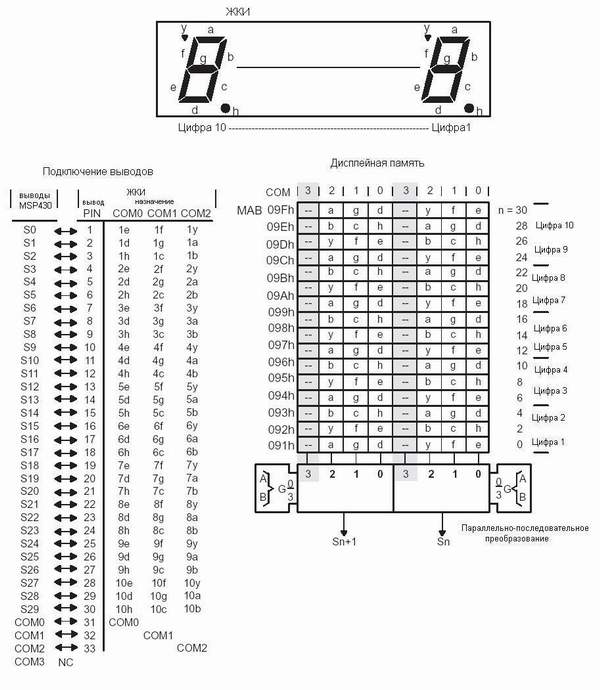

На рис. 18-9 показан пример ЖКИ в режиме тройного мультиплексирования, его подключение к MSP430 и карта сегментов. Обратите внимание, что это всего лишь пример, реальная карта сегментов в каждом конкретном случае будет зависеть от расположения выводов ЖКИ и его подключения к MSP430.

Рис. 18-9 Пример ЖКИ в режиме тройного мультиплексирования

Пример программы для режима тройного мультиплексирования

; При тройном мультиплексировании поддерживается 9

; сегментов для каждой цифры. Они расположены

; в 1 1/2 байтах дисплейной памяти.

a EQU 0040h

b EQU 0400h

c EQU 0200h

d EQU 0010h

e EQU 0001h

f EQU 0002h

g EQU 0020h

h EQU 0100h

y EQU 0004h

; Будет отображаться младшая цифра из регистра Rx.

; Таблица представляет включенные сегменты в соответствии

; с младшей цифрой регистра Rx.

; Регистр Ry используется в служебных целях

ODDDIG RLA Rx ; ЖКИ в режиме тройного мультиплексирования

; имеет 9 сегментов на цифру; для отображаемых

; символов требуется 16-битная таблица.

MOV Table(Rx),Ry ; Загрузка информации о сегментах

; в служебную память.

; (Ry) = 0000 0bch 0agd 0yfe

MOV.B Ry,&LCDn ; записывает сегменты ’a, g, d, y, f, e’

; Цифры № n (младший байт)

SWPB Ry ; (Ry) = 0agd 0yfe 0000 0bch

BIC.B #07h,&LCDn+1 ; записывает сегменты ’b, c, h’

; Цифры № n (старший байт)

BIS.B Ry,&LCDn+1

.....

EVNDIG RLA Rx ; ЖКИ в режиме тройного мультиплексирования

; имеет 9 сегментов на цифру; для отображаемых

; символов требуется 16-битная таблица.

MOV Table(Rx),Ry ; Загрузка информации о сегментах

; в служебную память.

; (Ry) = 0000 0bch 0agd 0yfe

RLA Ry ; (Ry) = 0000 bch0 agd0 yfe0

RLA Ry ; (Ry) = 000b ch0a gd0y fe00

RLA Ry ; (Ry) = 00bc h0ag d0yf e000

RLA Ry ; (Ry) = 0bch 0agd 0yfe 0000

BIC.B #070h,&LCDn+1

BIS.B Ry,&LCDn+1 ; записывает сегменты ’y, f, e’

; Цифры № n+1 (младший байт)

SWPB Ry ; (Ry) = 0yfe 0000 0bch 0agd

MOV.B Ry,&LCDn+2 ; записывает сегменты ’b, c, h, a, g, d’

; Цифры № n+1 (старший байт)

...........

Table DW a+b+c+d+e+f ; отображает ”0”

DW b+c ; отображает ”1”

...........

DW a+e+f+g ; отображает ”F”

18.2.9 Режим четырёхкратного мультиплексирования (4-Mux)

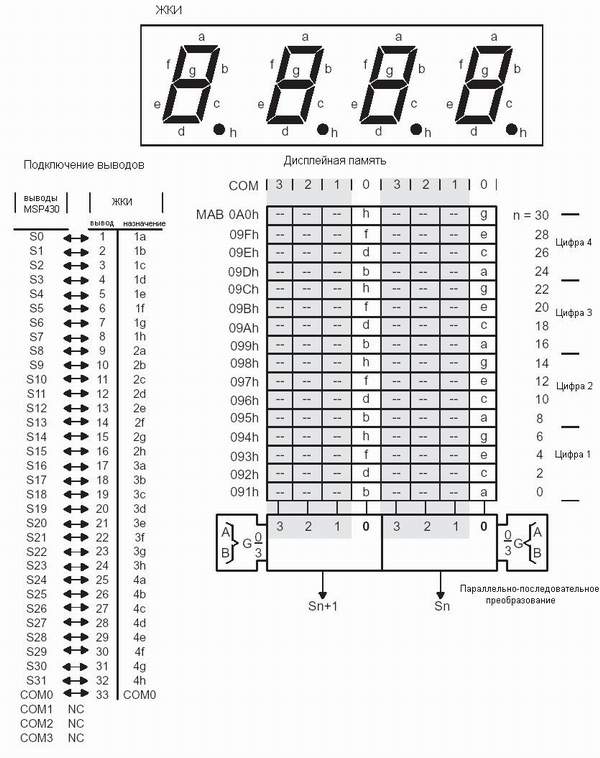

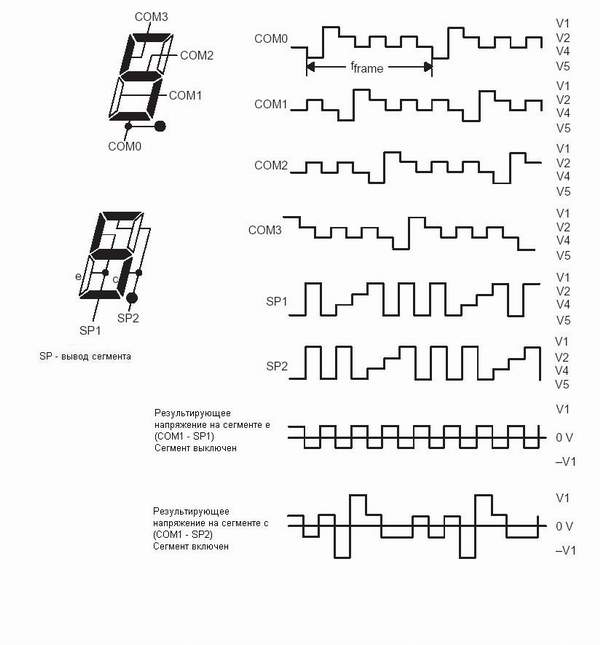

В режиме четырёхкратного мультиплексирования каждый сегментный выход микроконтроллера MSP430 управляет четырьмя сегментами ЖКИ, при этом используются все четыре линии строк, COM0, COM1, COM2 и COM3. На Рис. 18–10 показаны примеры осциллограмм сигналов в режиме четырёхкратного мультиплексирования.

Рис. 18–10 Примеры осциллограмм сигналов в режиме четырёхкратного мультиплексирования

На рис. 18-11 показан пример ЖКИ в режиме четырёхкратного мультиплексирования, его подключение к MSP430 и карта сегментов. Обратите внимание, что это всего лишь пример, реальная карта сегментов в каждом конкретном случае будет зависеть от расположения выводов ЖКИ и его подключения к MSP430.

Рис. 18-11 Пример ЖКИ в режиме четырёхкратного мультиплексирования

Пример программы для режима четырёхкратного мультиплексирования

; В режиме четырёхкратного мультиплексирования

; поддерживается восемь сегментов для каждой цифры.

; Все восемь сегментов для каждой цифры,

; как правило, расположены в одном байте дисплейной памяти

a EQU 080h

b EQU 040h

c EQU 020h

d EQU 001h

e EQU 002h

f EQU 008h

g EQU 004h

h EQU 010h

;

; Будет отображаться младшая цифра из регистра Rx.

; Таблица представляет включенные сегменты в соответствии

; с младшей цифрой регистра Rx.

;

MOV.B Table(Rx),&LCDn ; n = 1 ..... 15

; все восемь сегментов

; записываются

; в дисплейную память

...........

...........

Table DB a+b+c+d+e+f ; отображает ”0”

DB b+c ; отображает ”1”

...........

...........

DB b+c+d+e+g ; отображает ”d”

DB a+d+e+f+g ; отображает”E”

DB a+e+f+g ; отображает ”F”

18.3 Регистры модуля контроллера ЖКИ

Регистры модуля контроллера ЖКИ перечислены в таблице 18–1.

Таблица 18–1

| Регистр |

Краткое название |

Тип |

Адрес |

Начальное состояние |

| Регистр управления контроллером модуля ЖКИ |

LCDCTL1 |

Чтение/запись |

090h |

Обнулён по сбросу PUC |

| Регистр дисплейной памяти 1 |

LCDM1 |

Чтение/запись |

091h |

Не изменяется |

| Регистр дисплейной памяти 2 |

LCDM2 |

Чтение/запись |

092h |

Не изменяется |

| Регистр дисплейной памяти 3 |

LCDM3 |

Чтение/запись |

093h |

Не изменяется |

| Регистр дисплейной памяти 4 |

LCDM4 |

Чтение/запись |

094h |

Не изменяется |

| Регистр дисплейной памяти 5 |

LCDM5 |

Чтение/запись |

095h |

Не изменяется |

| Регистр дисплейной памяти 6 |

LCDM6 |

Чтение/запись |

096h |

Не изменяется |

| Регистр дисплейной памяти 7 |

LCDM7 |

Чтение/запись |

097h |

Не изменяется |

| Регистр дисплейной памяти 8 |

LCDM8 |

Чтение/запись |

098h |

Не изменяется |

| Регистр дисплейной памяти 9 |

LCDM9 |

Чтение/запись |

09Ah |

Не изменяется |

| Регистр дисплейной памяти 10 |

LCDM10 |

Чтение/запись |

09Bh |

Не изменяется |

| Регистр дисплейной памяти 11 |

LCDM11 |

Чтение/запись |

09Ch |

Не изменяется |

| Регистр дисплейной памяти 12 |

LCDM12 |

Чтение/запись |

09Dh |

Не изменяется |

| Регистр дисплейной памяти 13 |

LCDM13 |

Чтение/запись |

09Eh |

Не изменяется |

| Регистр дисплейной памяти 14 |

LCDM14 |

Чтение/запись |

09Fh |

Не изменяется |

| Регистр дисплейной памяти 15 |

LCDM15 |

Чтение/запись |

0A0h |

Не изменяется |

| Регистр дисплейной памяти 16 |

LCDM16 |

Чтение/запись |

0A1h |

Не изменяется |

| Регистр дисплейной памяти 17 |

LCDM17 |

Чтение/запись |

0A2h |

Не изменяется |

| Регистр дисплейной памяти 18 |

LCDM18 |

Чтение/запись |

0A3h |

Не изменяется |

| Регистр дисплейной памяти 19 |

LCDM19 |

Чтение/запись |

0A4h |

Не изменяется |

| Регистр дисплейной памяти 20 |

LCDM20 |

Чтение/запись |

0A5h |

Не изменяется |

LCDCTL1, Регистр управления контроллером модуля ЖКИ

| LCDPx |

LCDMXx |

LCDSON |

Не исполь

зуется |

LCDON |

| rw-0 |

rw-0 |

rw-0 |

rw-0 |

rw-0 |

rw-0 |

rw-0 |

rw-0 |

| LCDPx |

Биты 7-5 |

Выбор портов модуля контроллера ЖКИ. Эти биты определяют функцию вывода - выходной сигнал контроллера ЖКИ или порт ввода/вывода. Биты влияют ТОЛЬКО на выводы с мультиплексируемыми функциями. Обособленные выводы контроллера ЖКИ всегда сохраняют свою функцию.

000 Нет мультиплексируемых выводов с функцией выхода контроллера ЖКИ

001 S0-S15 - выходы контроллера ЖКИ

010 S0-S19 - выходы контроллера ЖКИ

011 S0-S23 - выходы контроллера ЖКИ

100 S0-S27 - выходы контроллера ЖКИ

101 S0-S31 - выходы контроллера ЖКИ

110 S0-S35 - выходы контроллера ЖКИ

111 S0-S39 - выходы контроллера ЖКИ |

| LCDMXx |

Биты 4-3 |

Выбор режима мультиплексии. Этими битами определяется режим работы ЖКИ.

00 Статический

01 Двойная мультиплексия (2-mux)

10 Тройная мультиплексия (3-mux)

11 Четырёхкратная мультиплексия (4-mux) |

| LCDSON |

Бит 2 |

Включение сегментов ЖКИ. Этим битом реализуется режим мигания. При этом татковый генератор ЖКИ и R33 остаются включенными, а все сегменты выключаются.

0 Все сегменты ЖКИ выключены

1 Сегменты ЖКИ включены либо выключены в зависимости от настроек дисплейной памяти |

| Не используется |

Бит 1 |

Не используется |

| LCDON |

Бит 0 |

Включение контроллера ЖКИ. Этим битом управляются тактовый генератор и R33.

0 - тактовый генератор и R33 выключены

1 - тактовый генератор и R33 включены |

|