Раздел 16

Модуль операционного усилителя ОА

Модуль ОА представляет собой операционный усилитель общего назначения. В этой главе описана работа модуля ОА. Модуль операционного усилителя ОА присутствует в микроконтроллерах MSP430FG43x.

Содержание:

16.1 Модуль операционного усилителя ОА - введение

Модуль операционного усилителя ОА предназначен для обработки аналоговых сигналов для последующего аналогово-цифрового преобразования. Модуль обладает следующими свойствами:

- Питание от одного источника, низкое энергопотребление

- Размах выходного сигнала от положительного до отрицательного напряжения питания (Rail-To-Rail Output).

- Программно устанавливаемый размах входного сигнала от положительного до отрицательного напряжения питания (Rail-To-Rail Input).

- Программно выбираемое соотношение между временем установления и энергопотреблением.

- Программно выбираемая конфигурация

- Программно выбираемый резистор обратной связи позволяет создавать усилители с программируемым коэффициентом усиления (PGA).

|

Примечание: несколько модулей ОА

Некоторые микроконтроллеры могут содержать более одного модуля ОА. В таких случаях все модули ОА имеют одинаковые характеристики. В данной главе описания модулей и регистров даются в виде OAxCTL0, где х обозначает порядковый номер модуля. Если порядковый номер приведен, то описание относится к конкретному модулю. В случае, когда модули идентичны, названия регистров будут иметь вид OAxCTL0.

|

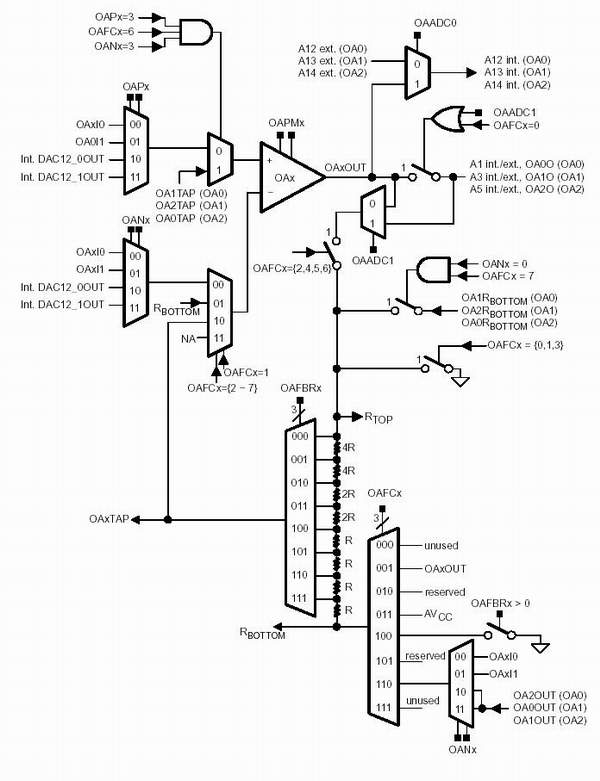

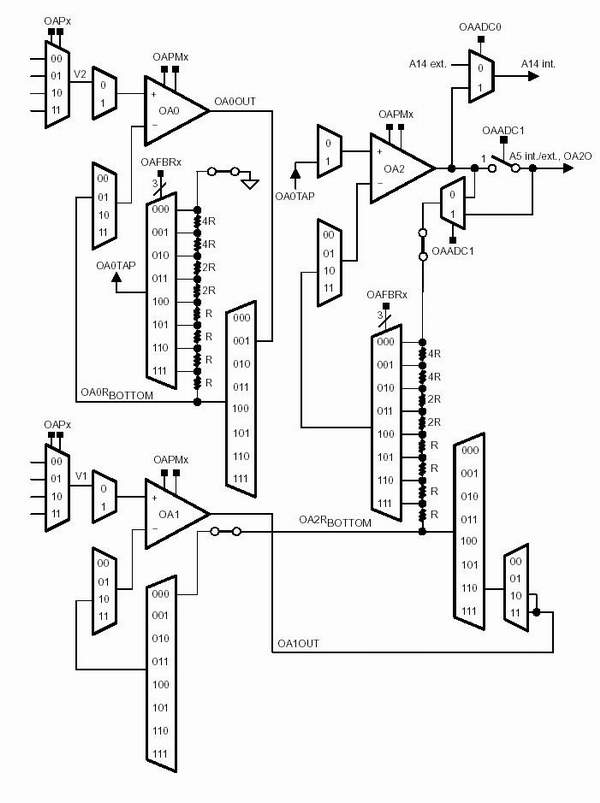

Блок схема модуля операционного усилителя ОА показана на рис. 16–1.

Рис. 16-1. Блок схема модуля операционного усилителя ОА

16.2 Работа модуля операционного усилителя ОА

Модуль OA конфигурируется при помощи пользовательского программного обеспечения. Настройка и функционирование модуля будут подробно рассмотрены ниже.

16.2.1 Усилитель ОА

Модуль ОА представляет собой конфигурируемый, низкопотребляющий усилитель с широким диапазоном входных и выходных сигналов. Он может быть сконфигурирован как инвертирующий или неинвертирующий усилитель, либо, в комбинации с другими модулями ОА может составлять дифференциальный усилитель. Скорость нарастания выходного сигнала регулируется программно с помощью бит OAPMx с целью минимизации потребляемого тока при требуемом времени установления. Когда OAPMx =0, операционный усилитель выключен, а его выход находится в высокоимпедансном состоянии. Когда OAPMx >0, операционный усилитель включен. См. параметры модуля в документации на конкретный МК.

16.2.2 Вход ОА

Модуль ОА имеет конфигурируемые входы. Сигналы, подаваемые на инвертирующий (« - ») и неинвертирующий (« + ») входы индивидуально выбираются битами OANx и OAPx соответственно. Они могут быть как внешними, так и внутренними – сиганлами с одного из модулей ЦАП DAC12. Один из неинвертирующих входов объединён у всех модулей ОА. Диапазон входного сигнала модуля ОА программно выбирается битом OARRIP. Когда OARRIP =0, диапазон входного сигнала может лежать во всём диапазоне от «+» до «-» питания (rail-to-rail input mode), потребление усилителя при этом увеличивается. См. параметры модуля в документации на конкретный МК.

16.2.3 Выход ОА

Модуль ОА имеет конфигурируемый выход. Сигналы с выхода ОА могут подаваться на входы A12 (OA0), A13 (OA1) и A14 (OA2) модуля АЦП ADC12 с помощью бита OAADC0. Когда OAADC =1, выход ОА подключен ко входу АЦП непосредственно внутри микроконтроллера, внешний вход АЦП при этом отключен. Сигналы с выхода ОА могут подаваться на входы A1 (OA0), A3 (OA1) и A5 (OA2) модуля АЦП если OAFCx=0 или OAADC1 =1. В этом случае, выход ОА подключен как ко входу АЦП, так и к внешнему выводу. Выход ОА также подключается к цепочке резисторов при помощи бита OAFCx. Для обеспечения требуемого усиления битами OAFBRx выбирается требуемый резистор из цепочки.

16.2.4 Конфигурация OA

Модуль OA может быть сконфигурирован для различных режимов работы с помощью бит OAFCx в соответствии с Таблицей 16-1.

Таблица 16-1. Выбор режима ОА

| OAFCx |

Режим ОА |

| 000 |

ОУ общего назначения |

| 001 |

Буфер с единичным усилением |

| 010 |

Зарезервирован |

| 011 |

Компаратор |

| 100 |

Неинвертирующий усилитель с программируемым коэффициентом усиления (PGA) |

| 101 |

Зарезервирован |

| 110 |

Инвертирующий усилитель с программируемым коэффициентом усиления (PGA) |

| 111 |

Дифференциальный усилитель |

Режим операционного усилителя общего назначения

В этом режиме цепочка резисторов обратной связи отключена от OAx, а биты регистра OAxCTL0 определяют подключение сигналов. Входы модулей OAx выбираются битами OAPx и OANx . Выход модуля OAx подключен ко входу, выбираемому битами регистра OAxCTL0, АЦП ADC12 внутри микроконтроллера.

Режим буфера с единичным усилением

В этом режиме выход операционного усилителя подключен к верхнему резистору RTOP из цепочки обратной связи и к инвертирующему входу ОУ, формируя буфер с единичным усилением. Подключение неинвертирующего входа определяется битом OAPx. Внешнее подключение инвертирующего входа отключено, бит OANx игнорируется. Выход модуля OAx подключен ко входу, выбираемому битами регистра OAxCTL0, АЦП ADC12 внутри микроконтроллера.

Режим компаратора

В этом режиме цепочка резисторов обратной связи отключена от OAx. Верхний резистор из цепочки обратной связи RTOP подключен к AVSS, а нижний RBOTTOM - к AVCC. Сигнал OaxTAP подключен к инвертирующему входу ОА, формируя, таким образом, компаратор с программируемым порогом. Порог срабатывания определяется битами OAFBRx, а подключение неинвертирующего входа определяется битом OAPx. Дополнительно, можно сформировать гистерезис при помощи внешнего резистора положительной обратной связи. Внешнее подключение инвертирующего входа отключено, бит OANx игнорируется. Выход модуля OAx подключен ко входу, выбираемому битами регистра OAxCTL0, АЦП ADC12 внутри микроконтроллера.

Режим неинвертирующего усилителя с программируемым коэффициентом усиления (PGA)

В этом режиме выход ОА подключен к верхнему резистору цепочки обратной связи RTOP, а нижний резистор цепочки обратной связи RBOTTOM подключен к AVSS. Сигнал OaxTAP подключен к неинвертирующему входу ОА, формируя, таким образом, неинвертирующий усилитель с программируемым усилением, равным [1+ отношение OAxTAP]. Отношение OAxTAP определяется битами OAFBRx. Если OAFBRx = 0, усиление равно единице. Подключение неинвертирующего входа определяется битом OAPx. Внешнее подключение инвертирующего входа отключено, бит OANx игнорируется. Выход модуля OAx подключен ко входу, выбираемому битами регистра OAxCTL0, АЦП ADC12 внутри микроконтроллера.

Режим инвертирующего усилителя с программируемым коэффициентом усиления (PGA)

В этом режиме выход ОА подключен к верхнему резистору цепочки обратной связи RTOP, а нижний резистор цепочки обратной связи RBOTTOM подключен к аналоговому мультиплексору, который подключает этот вывод к IN0N, IN1N или выходу остальных модулей ОА. Управление осуществляется битами OANx. Сигнал OAxTAP подключен к инвертирующему входу ОА, формируя, таким образом, инвертирующий усилитель с программируемым усилением, равным [минус отношение OAxTAP]. Отношение OAxTAP определяется битами OAFBRx. Подключение неинвертирующего входа определяется битом OAPx. Выход модуля OAx подключен ко входу, выбираемому битами регистра OAxCTL0, АЦП ADC12 внутри микроконтроллера.

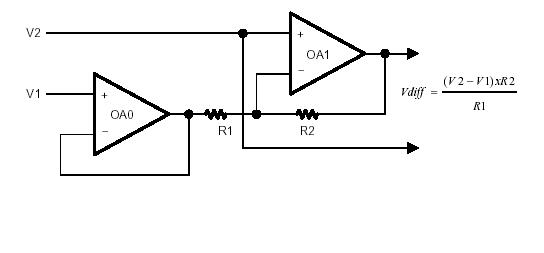

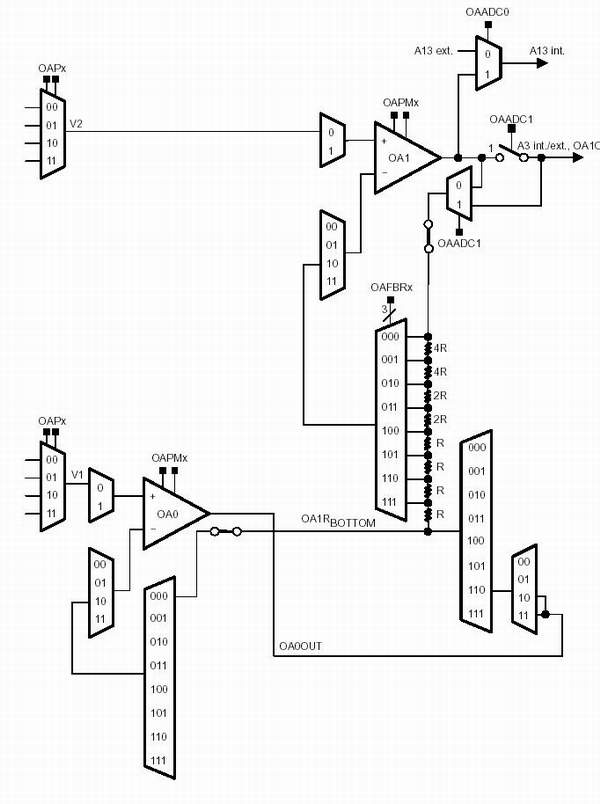

Режим дифференциального усилителя

Этот режим позволяет соединять внутри микроконтроллера сигналы двух или трёх модулей ОА. На рис. 16-2 изображено подключение двух модулей ОА – ОА0 и ОА1. Выход модуля OAx подключен к верхнему резистору цепочки обратной связи RTOP и второму модулю ОАх в режиме инвертирующего усилителя с программируемым коэффициентом усиления. Нижний резистор цепочки обратной связи RBOTTOM остаётся неподключенным, при этом образуется буфер с единичным усилением. Данный буфер в комбинации с одним или двумя оставшимися модулями ОАх формируют дифференциальный усилитель. Выход модуля OAx подключен ко входу, выбираемому битами регистра OAxCTL0, АЦП ADC12 внутри микроконтроллера. На рис. 16-2 показан пример формирования дифференциального усилителя с использованием двух модулей ОА – ОА0 и ОА1. Параметры управляющих регистров даны в Таблице 16-2. Усиление определяется битами OAFBRx для ОА1 и приведено в Таблице 16-3. Внутренние подключения между модулями ОА показаны на рис. 16-3.

Таблица 16-2. Настройки регистров управления для дифференциального усилителя на базе двух ОУ.

| Регистр |

Настройки (в двоичном виде) |

| OA0CTL0 |

00 xx xx 0 0 |

| OA0CTL1 |

000 111 0 x |

| OA1CTL0 |

10 xx xx x x |

| OA1CTL1 |

xxx 110 0 x |

Таблица 16-3. Параметры усиления для дифференциального усилителя на базе двух ОУ.

| OA1 OAFBRx |

Усиление |

| 000 |

0 |

| 001 |

1/3 |

| 010 |

1 |

| 011 |

1 2/3 |

| 100 |

3 |

| 101 |

4 1/3 |

| 110 |

7 |

| 111 |

15 |

Рис. 16-2. Дифференциальный усилитель на базе двух ОУ

Рис. 16-3. Внутренние соединения дифференциального усилителя на базе двух ОУ

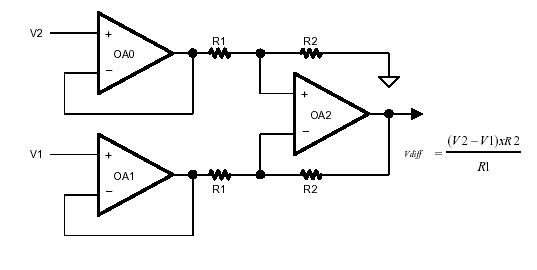

На рис. 16-4 показан пример формирования дифференциального усилителя с использованием трёх модулей ОА – ОА0, ОА1 и ОА2. Параметры управляющих регистров даны в Таблице 16-4. Усиление определяется битами OAFBRx для ОА0 и ОА2. Настройки бит OAFBRx должны быть идентичными для обоих модулей ОА0 и ОА2. Параметры усиления приведены в Таблице 16-5. Внутренние подключения между модулями ОА показаны на рис. 16-5.

Таблица 16-4. Настройки регистров управления для дифференциального усилителя на базе трёх ОУ.

| Регистр |

Настройки (в двоичном виде) |

| OA0CTL0 |

00 xx xx 0 0 |

| OA0CTL1 |

xxx 001 0 x |

| OA1CTL0 |

00 xx xx 0 0 |

| OA1CTL1 |

000 111 0 x |

| OA2CTL0 |

11 11 xx x x |

| OA2CTL1 |

xxx 110 0 x |

Таблица 16-5. Параметры усиления для дифференциального усилителя на базе трёх ОУ.

| OA0/ОА2 OAFBRx |

Усиление |

| 000 |

0 |

| 001 |

1/3 |

| 010 |

1 |

| 011 |

1 2/3 |

| 100 |

3 |

| 101 |

4 1/3 |

| 110 |

7 |

| 111 |

15 |

Рис. 16-4. Дифференциальный усилитель на базе трёх ОУ

Рис. 16-5. Внутренние соединения дифференциального усилителя на базе трёх ОУ

16.3 Регистры модуля операционного усилителя ОА

Регистры модуля операционного усилителя ОА перечислены в таблице 16–6.

Таблица 16–6

| Регистр |

Краткое название |

Тип |

Адрес |

Начальное состояние |

| Модуль ОА0 регистр управления 0 |

ОA0CTL0 |

Чтение/запись |

0C0h |

Обнулён по сбросу PUC |

| Модуль ОА0 регистр управления 1 |

ОA0CTL1 |

Чтение/запись |

0C1h |

Обнулён по сбросу PUC |

| Модуль ОА1 регистр управления 0 |

ОA1CTL0 |

Чтение/запись |

0C2h |

Обнулён по сбросу PUC |

| Модуль ОА1 регистр управления 1 |

ОA1CTL1 |

Чтение/запись |

0C3h |

Обнулён по сбросу PUC |

| Модуль ОА2 регистр управления 0 |

ОA2CTL0 |

Чтение/запись |

0C4h |

Обнулён по сбросу PUC |

| Модуль ОА2 регистр управления 1 |

ОA2CTL1 |

Чтение/запись |

0C5h |

Обнулён по сбросу PUC |

ОAxCTL0, регистр управления операционным усилителем 0

| OANx |

OAPx |

OAPMx |

OAADC1 |

OAADC0 |

| rw-0 |

rw-0 |

rw-0 |

rw-0 |

rw-0 |

rw-0 |

rw-0 |

rw-0 |

| OANx |

Биты 7-6 |

Выбор подключения инвертирующего входа. Эти биты определяют входной сигнал для инвертирующего входа ОУ.

00 OAxI0

01 OAxI1

10 DAC0 встроенный

11 DAC1 встроенный |

| OAPx |

Биты 5-4 |

Выбор подключения неинвертирующего входа. Эти биты определяют входной сигнал для неинвертирующего входа ОУ.

00 OAxI0

01 OAxI1

10 DAC0 встроенный

11 DAC1 встроенный |

| OAPMx |

Биты 3-2 |

Выбор скорости нарастания выходного сигнала. Этими битами определяется соотношение между скоростью нарастания выходного сигнала и потребляемым током ОУ.

00 Выключен, выход в высокоимпедансном состоянии

01 Медленная

10 Средняя

11 Быстрая |

| OAADC1 |

Бит 1 |

Выбор подключения выхода ОУ. Этим битом управляется подключение выхода модуля OAx ко входу Ax модуля АЦП ADC12 при OAFCx > 0.

0 - выход модуля OAx не подключен к A1 (OA0), A3 (OA1), или A5 (OA2)

1 - выход модуля OAx подключен к A1 (OA0), A3 (OA1), или A5 (OA2) |

| OAADC0 |

Бит 0 |

Выбор подключения выхода ОУ. Этим битом управляется подключение выхода модуля OAx ко входу Ax модуля АЦП ADC12.

0 - выход модуля OAx не подключен к A12 (OA0), A13 (OA1), или A14 (OA2)

1 - выход модуля OAx подключен к A12 (OA0), A13 (OA1), или A14 (OA2) |

ОAxCTL1, регистр управления операционным усилителем 1

| OAFBRx |

OAFCx |

резер

вный |

OARRIP |

| rw-0 |

rw-0 |

rw-0 |

rw-0 |

rw-0 |

rw-0 |

rw-0 |

rw-0 |

| OAFBRx |

Биты 7-5 |

Выбор резистора обратной связи ОУ

000 Номинал 0

001 Номинал 1

010 Номинал 2

011 Номинал 3

100 Номинал 4

101 Номинал 5

110 Номинал 6

111 Номинал 7 |

| OAFCx |

Биты 4-2 |

Выбор функции ОУ. Эти биты определяют режим функционирования ОУ.

000 Общего назначения

001 Буфер с единичным усилением

010 Резервный

011 Компаратор

100 Неинвертирующий усилитель

101 Резервный

110 Инвертирующий усилитель

111 Дифференциальный усилитель |

| резервный |

Бит 1 |

резервный |

| OARRIP |

Бит 0 |

Отключение разрешения размаха входного сигнала от положительного до отрицательного напряжения питания (Rail-To-Rail Input).

0 - режим rail-to-rail включен

1 – размах входного сигнала ограничен. См. параметры в документации на конкретный МК. |

|